PX 697A

November 1958

Revised April, 1959

# Remington Rand Univac®

DIVISION OF SPERRY RAND CORPORATION UNIVAC PARK, ST. PAUL 16, MINNESOTA

#### TABLE OF CONTENTS

| Paragr | Title Title                                             | Page       |

|--------|---------------------------------------------------------|------------|

| 1.     | General                                                 | 1          |

| 2.     | Physical Description of Central Computer                | 3          |

| i      | a. General                                              | 3          |

| j      | o. Modular Breakdown                                    | 3          |

|        | Power Distribution                                      | 22         |

| (      | d. Signal Distribution                                  | 56         |

| (      | e. Corner Bays of Central Computer                      | 62         |

| 3. 1   | Electrical Description of Conventional Chassis Circuits | 64         |

| ;      | a. General                                              | 64         |

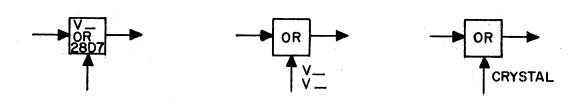

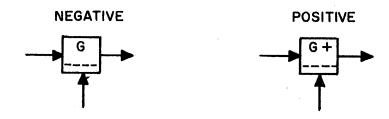

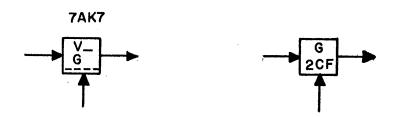

|        | o. Gates                                                | 64         |

|        | Flip-flops                                              | 71         |

| (      | l. Pulse Formers                                        | <b>7</b> 5 |

|        | e. Binary Counters                                      | 77         |

| 1      | f. Delay-flops                                          | 80         |

| 9      | Thyraflops                                              | 82         |

|        | Resistor-Comparator Circuits                            | 83         |

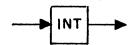

|        | . Delay Elements                                        | 85         |

|        | . Timing Pulse Generator and Timing Pulse Drivers       | 87         |

| I      | Adders                                                  | 91         |

| 4. I   | Clectrical Description of Printed-Circuit Chassis       | 101        |

| ā      | General                                                 | 101        |

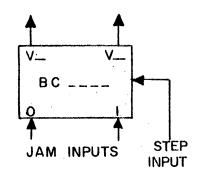

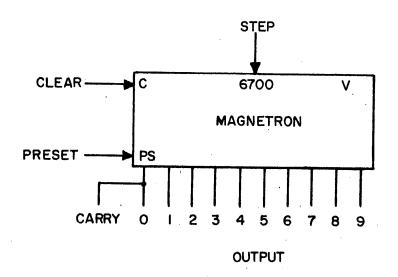

| ì      | Chassis Type 1, Magnetron Counter                       | 106        |

|        | . Chassis Type 2. Clear and Preset                      | 108        |

| C      | . Chassis Type 3, Digit Plane Control-rI                | 109        |

| €      | . Chassis Type 4. Digit Plane Control-r0                | 111        |

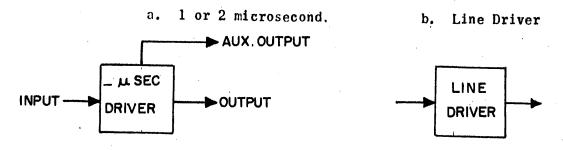

| 1      | Chassis Type 5. Line Driver                             | 113        |

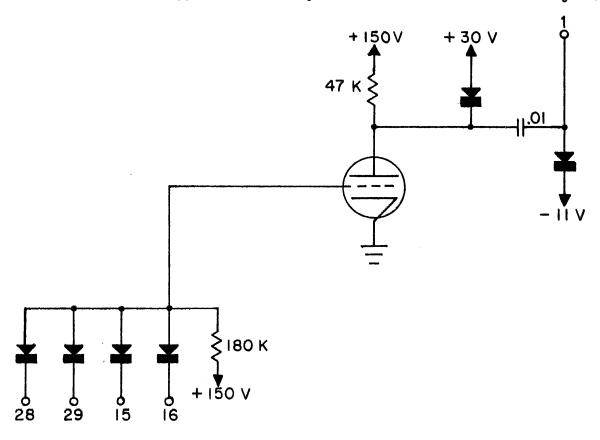

| Ç      | Chassis Type 6, 6146 Driver                             | 115        |

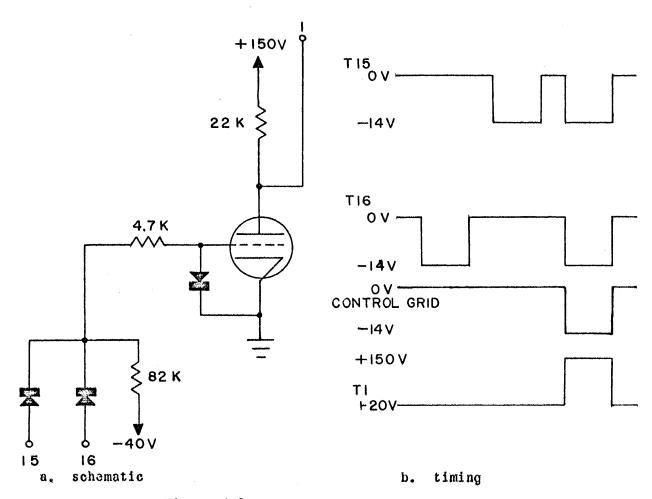

|        | . Chassis Type 7, Pulse Former, Positive                | 116        |

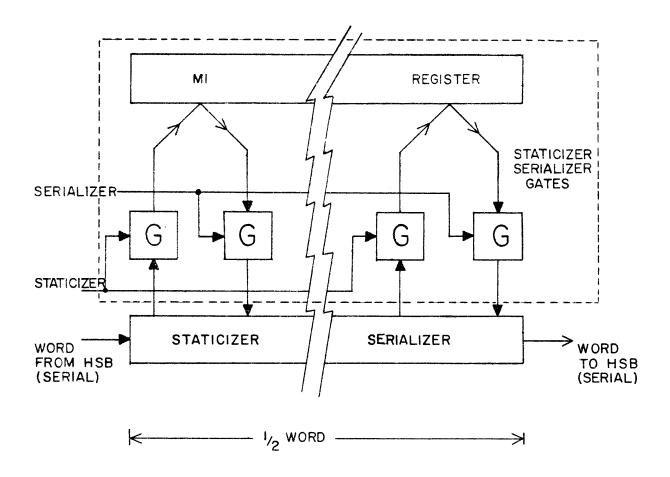

| j      | . Chassis Type 8. Staticizer-Serializer Gates           | 118        |

| j      | . Chassis Type 9, Amplifier Delay Line                  | 120        |

| _      | . Chassis Type 10, Delay Line                           | 121        |

| 1      | . Chassis Type 11, Flip-Flop                            | 121        |

| n      | Chassis Type 12, Sequencer                              | 122        |

| n      | . Chassis Type 13, Flip-Flop                            | 122        |

| C      | . Chassis Type 14, I-OEC Serializer                     | 122        |

|        | . Chassis Type 15. Output Distributor Gates             | 124        |

| -      | . Chassis Type 16, Universal Gating                     | 125        |

|        | . Chassis Type 17. Pulse Former. Negative               | 125        |

| S      | . Chassis Type 18, OR Inverter                          | 127        |

# TABLE OF CONTENTS (Cont.)

| Para | graph Title                                    | Page |

|------|------------------------------------------------|------|

| t.   | Chassis Type 19. Decoder Enable                | 128  |

| u.   |                                                | 129  |

| v.   |                                                | 130  |

| W.   |                                                | 132  |

| x.   | a                                              | 132  |

| y    |                                                | 133  |

| Z    |                                                | 135  |

| aa   |                                                | 136  |

| bb.  |                                                | 137  |

| cc,  |                                                | 137  |

| dd,  | •                                              | 139  |

| ee,  |                                                | 140  |

| ff   |                                                | 140  |

| 11,  | Itansiei Builei Biverver                       |      |

| 5.   | Protective Circuits of Central Computer        | 143  |

|      | a. General                                     | 143  |

|      | b. Protective Rectifiers                       | 143  |

|      | c. Power Fault Circuits                        | 144  |

|      | d. Interlock Circuits                          | 148  |

|      | e. Overheat Circuits                           | 150  |

| 6.   | Supervisory Control                            | 154  |

|      | a. General                                     | 154  |

|      | b. Supervisory Control Panel                   | 156  |

|      | c. Supervisory Control Keyboard                | 160  |

|      | d. Supervisory Control Printer                 | 161  |

|      |                                                | 162  |

|      | e. Supervisory Control Interconnections        | 163  |

|      | 1. Supervisory concret maintenance Equipment   |      |

| 7.   | UNISERVO II                                    | 164  |

|      | a. General                                     | 164  |

|      | b. Physical Description                        | 164  |

|      | c. Tape-handling System                        | 164  |

|      | d. Read/Write Head                             | 167  |

|      | · · · · · · · · · · · · · · · · · · ·          | 167  |

|      |                                                | 169  |

|      | , a a                                          | 169  |

|      | g. Cooling System                              | 169  |

|      | h. Integration of the Uniservo into the System | 181  |

|      | i. Operational Adjustments                     | 181  |

|      | j. Uniservo II - Final Operational Check List  | 181  |

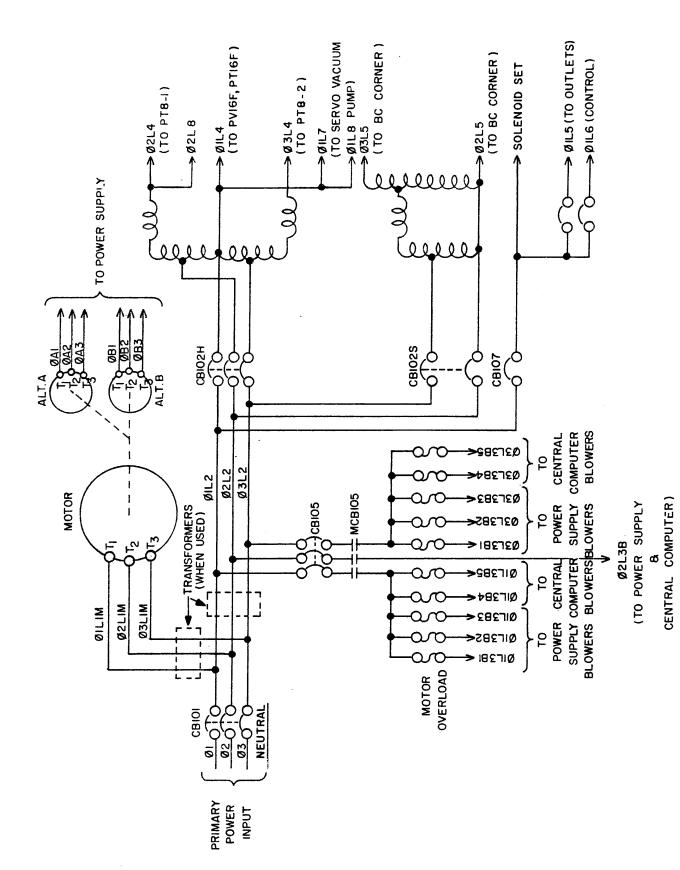

| 8.   | Power System                                   | 182  |

|      | a. General                                     | 182  |

|      | b. Switchgear                                  | 182  |

# TABLE OF CONTENTS (Cont.)

# 8. (Cont.)

| Par | <u>Title</u>                     | <u>Page</u>                                                                                    |

|-----|----------------------------------|------------------------------------------------------------------------------------------------|

|     | c. Power Supply                  | 227<br>238<br>256                                                                              |

| 9.  | Cooling                          | 262                                                                                            |

|     | a. General                       | 262                                                                                            |

| 10. | Univac II Maintenance Diagrams   | 264                                                                                            |

|     | a. General                       | 264<br>267                                                                                     |

|     | APPENDIX A                       |                                                                                                |

| Cha | sis Location Cross Index         | A-1                                                                                            |

|     | Bay A                            | A-2<br>A-3<br>A-4<br>A-5<br>A-6<br>A-9<br>A-12<br>A-15<br>A-17<br>A-18<br>A-19<br>A-20<br>A-21 |

| Mai | tenance Switches                 | B-1                                                                                            |

|     | Switches inside Central Computer | B-1<br>B-1                                                                                     |

| Mai | tenance Multivibrator            | C-1                                                                                            |

# TABLE OF CONTENTS (Cont.)

| Paragraph                                                                                                | <u>Title</u> | Page                                                 |

|----------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------|

| ı                                                                                                        | APPENDIX D   |                                                      |

| Memory Margin Test Procedures                                                                            |              | D-1                                                  |

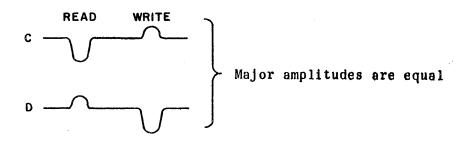

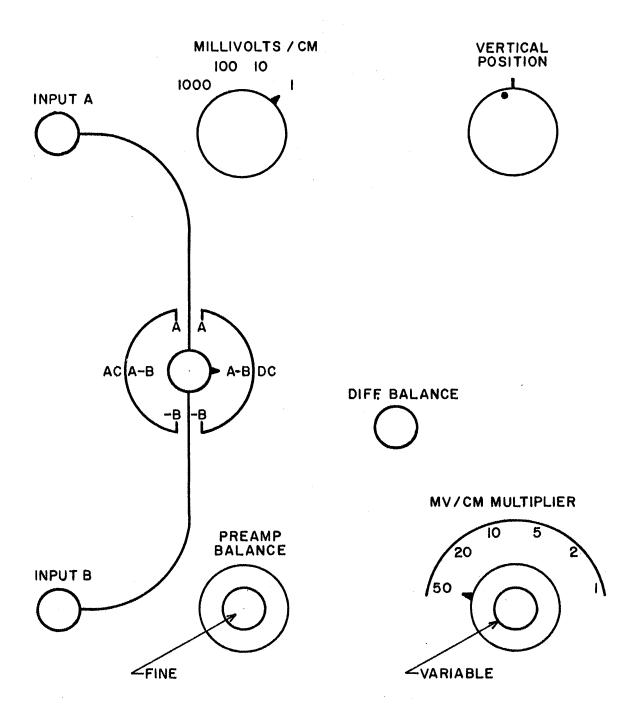

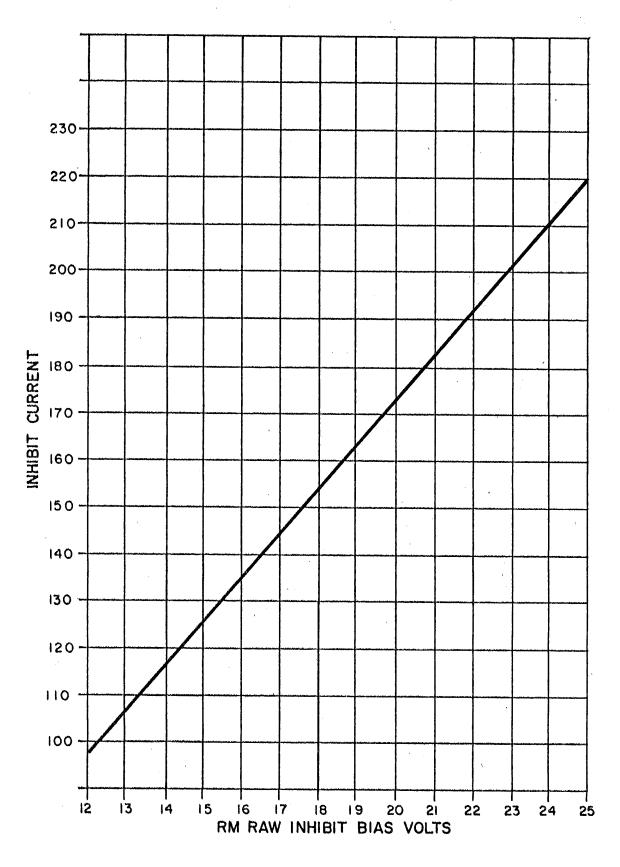

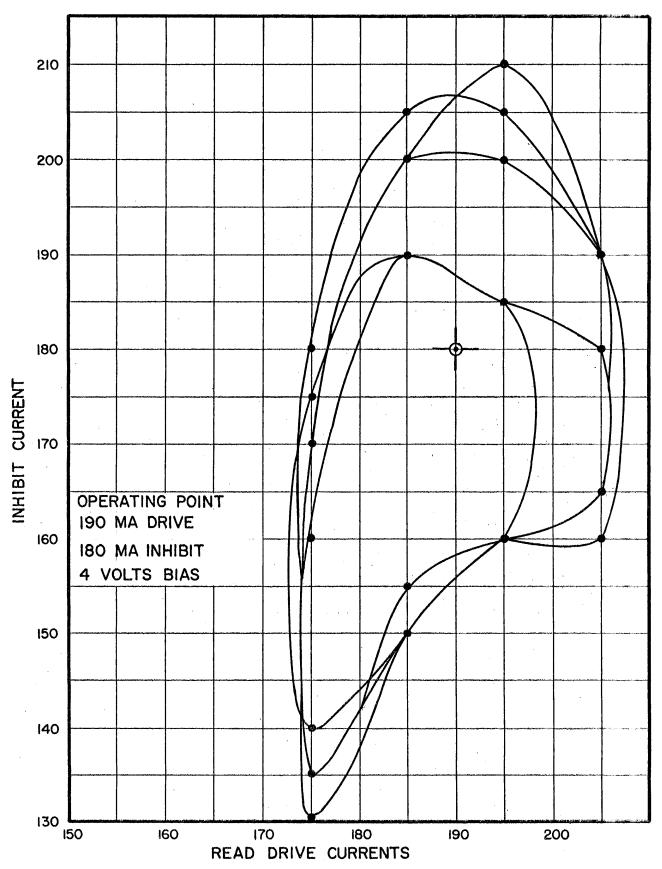

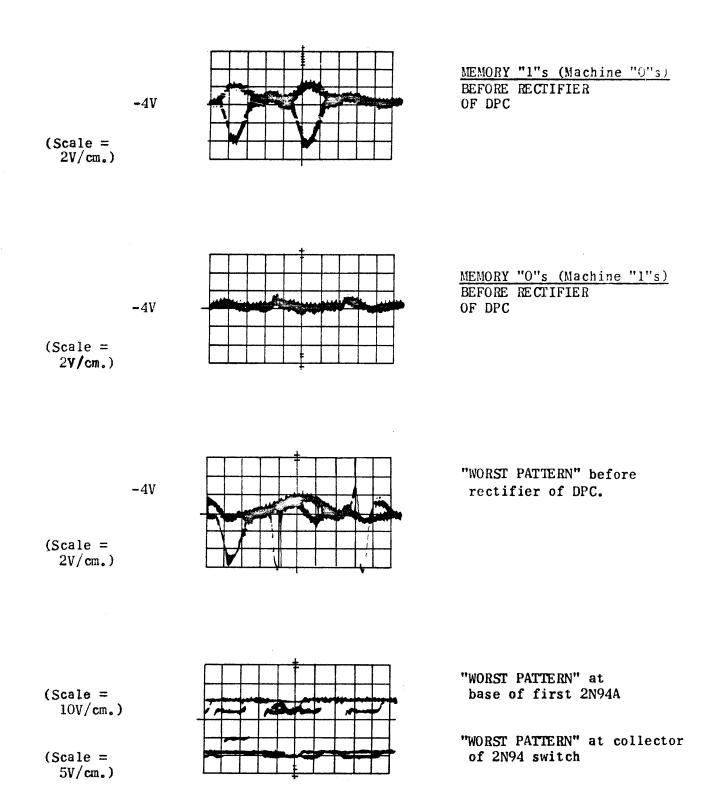

| Memory Margin Procedure Preventative Maintenance Procedure Idealized Waveforms Sense Amplifier Waveforms | cedure       | D-2<br>D-6<br>D-12<br>D-15<br>D-21                   |

| Suggested Maintenance Procedures                                                                         |              | E-1                                                  |

| Diodes                                                                                                   | APPENDIX F   | E-1<br>E-1<br>E-4<br>E-4<br>E-5<br>E-5<br>E-6<br>E-6 |

| Power Supply Adjustment                                                                                  |              | F-1                                                  |

|                                                                                                          | APPENDIX G   |                                                      |

| Input-Output Adjustment Criteria                                                                         |              | G-1                                                  |

#### LIST OF ILLUSTRATIONS

| <u>Figure</u> | <u>Title</u>                                                  | Page       |

|---------------|---------------------------------------------------------------|------------|

| 1-1.          | A Typical Central Computer Installation                       | 2          |

| 2-1.          | Bay Designations of Central Computer Group                    | 4          |

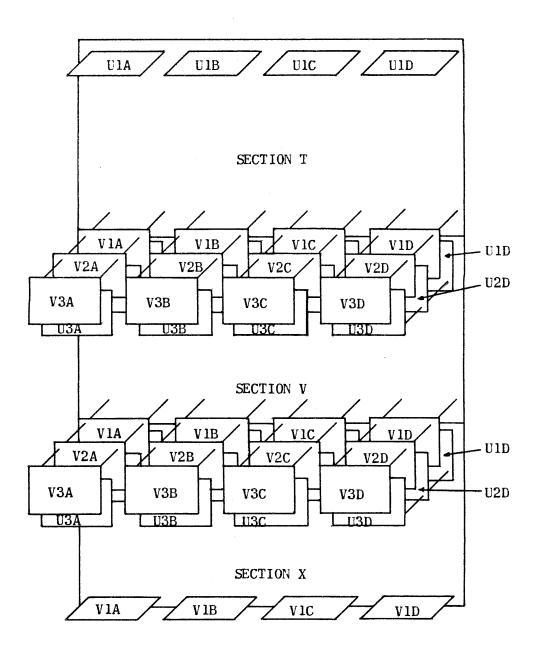

| 2-2.          | Typical Sections of Central Computer                          | 7          |

| 2-3.          | Typical Conventional Chassis                                  | 8          |

| 2-4.          | Location of Key Holes on the Conventional Chassis             | 11         |

| 2-5.          | Typical Printed-Circuit Chassis                               | 13         |

| 2-6.          | Bypass Board Locations                                        | 15         |

| 2-7.          | Section Edge Terminal Boards                                  |            |

| •             | (Bays A, B, C, D, GT, GX, H, J, K, L and P)                   | 17         |

| 2-8.          | Section Terminal Boards (Bays E. M. N and GV)                 | 18         |

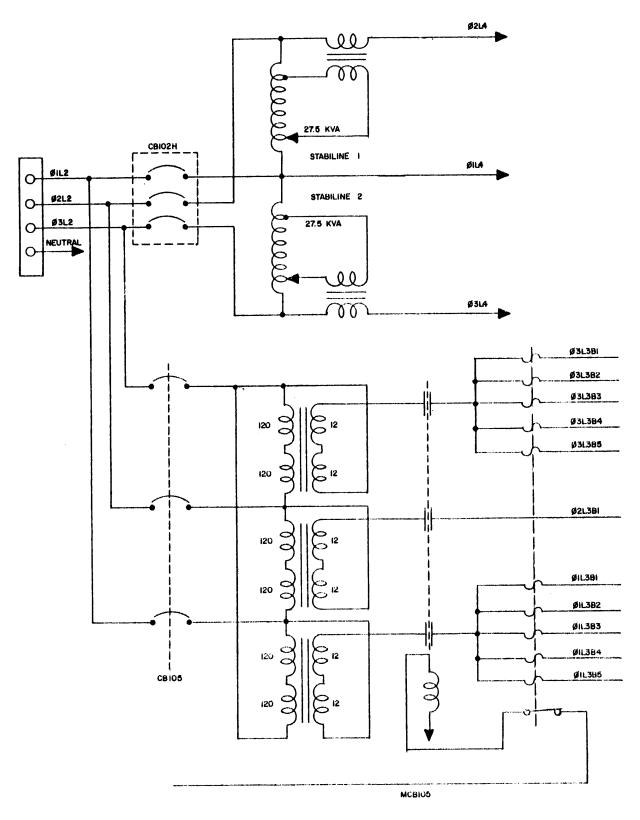

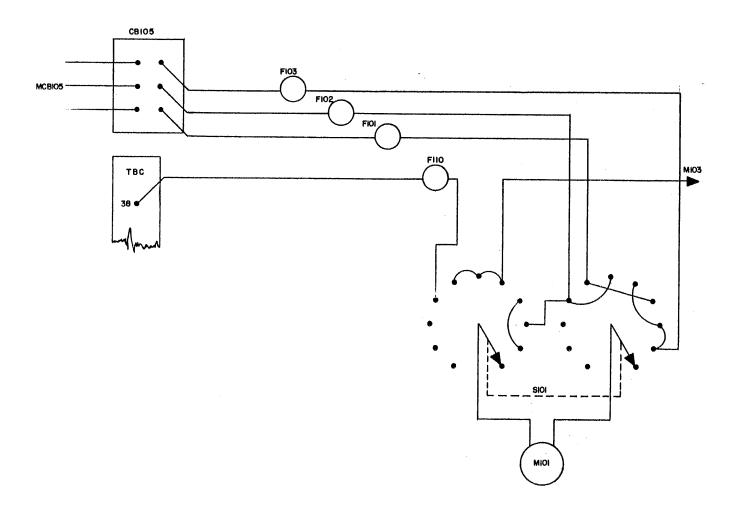

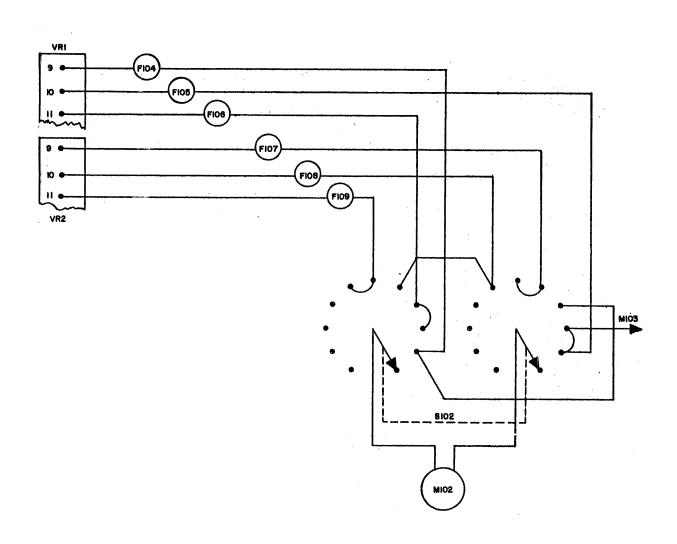

| 2-9.          | Designations of Primary Power Lines                           | 24         |

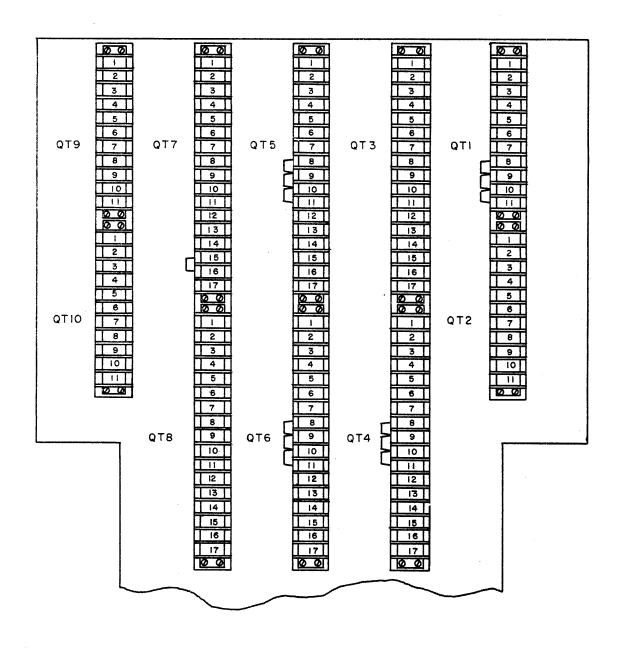

| 2-10.         | Quadrangle (Bay Q of Central Computer)                        | 26         |

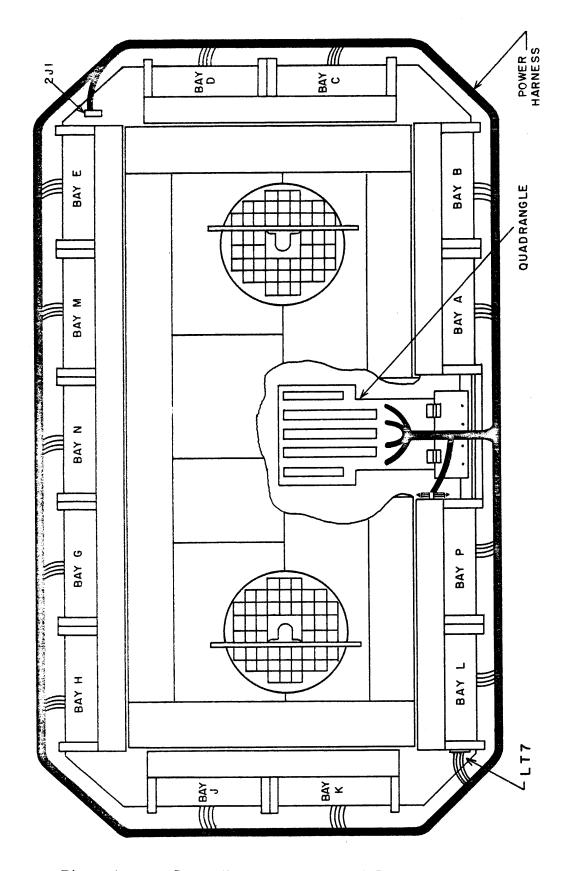

| 2-11.         | Power Harness at Base of Central Computer                     | 28         |

| 2-12.         | Barrier Strips of the Central Computer                        | 29         |

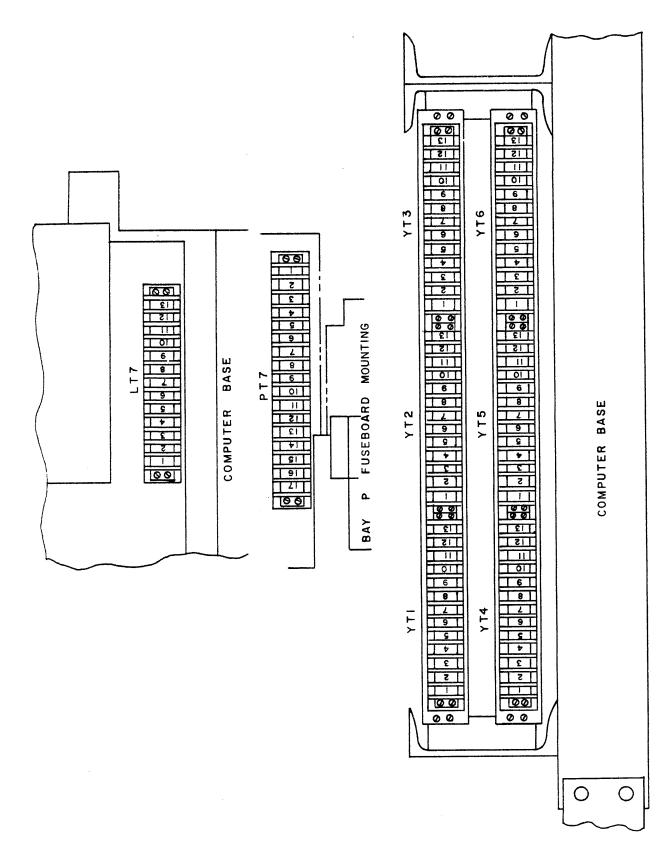

| 2-13.         | Filament Power Distribution to Bay P Fuseboards               | 30         |

| 2-14.         | Locations and Designations of Heater Transformer              | 33         |

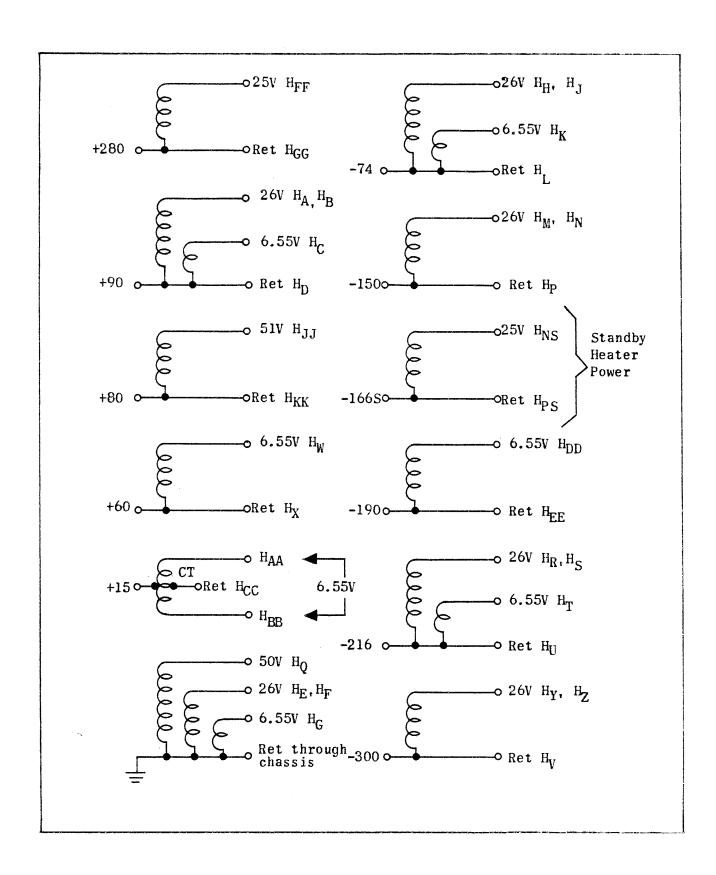

| 2-15.         | Heater Voltages Supplied to Central Computer                  | 35         |

| 2-16.         | Typical Filament Voltage Wiring                               | 36         |

| 2-17.         | Terminal and Spacer Boards of Tray Assembly                   | 61         |

|               |                                                               |            |

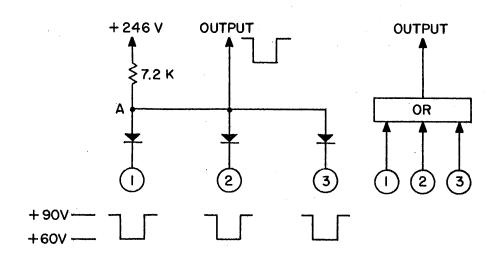

| 3-1.          | Typical Crystal Diode OR Gate                                 | 65         |

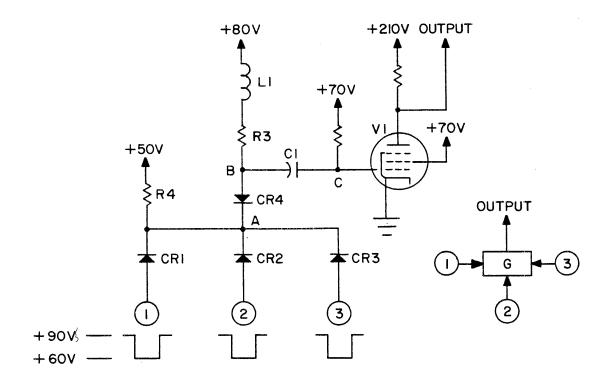

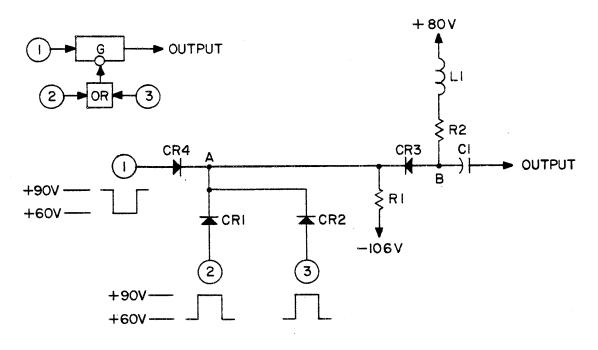

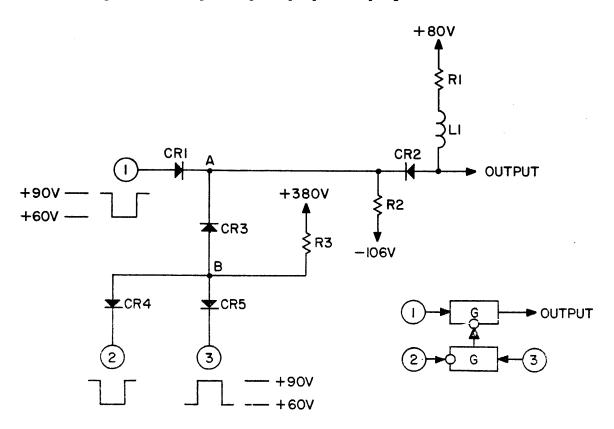

| 3-2.          | Typical Crystal Diode AND Gate                                | 66         |

| 3-3.          | Crystal Diode Delete Gate. Type I                             | 67         |

| 3-4.          | Crystal Delete Gate, Type II.                                 | 68         |

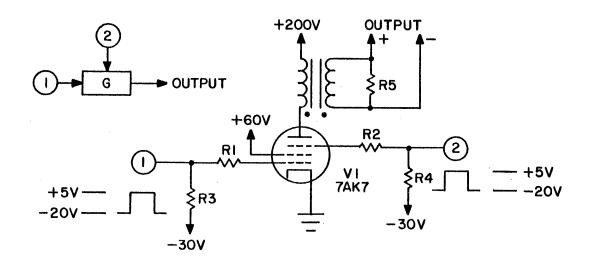

| 3-5.          | Schematic Diagram, Vacuum Tube AND Gate                       | 69         |

| 3-6.          | Schematic Diagram, Typical Clock Gate                         | 70         |

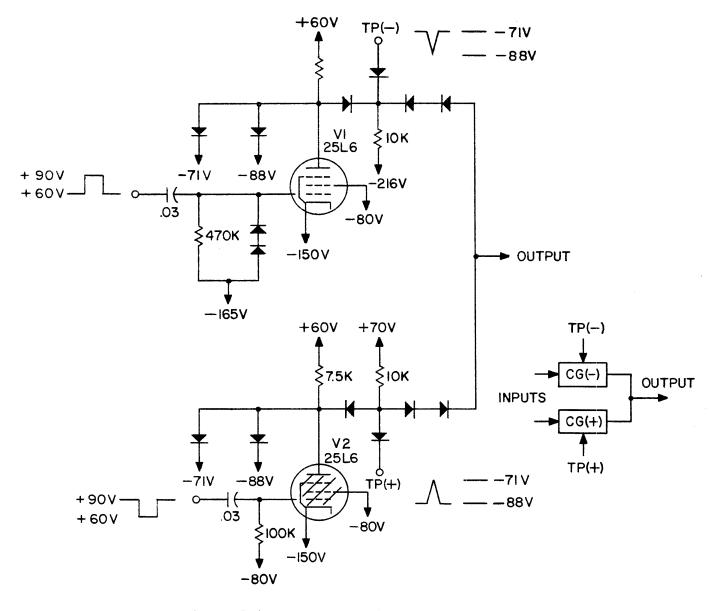

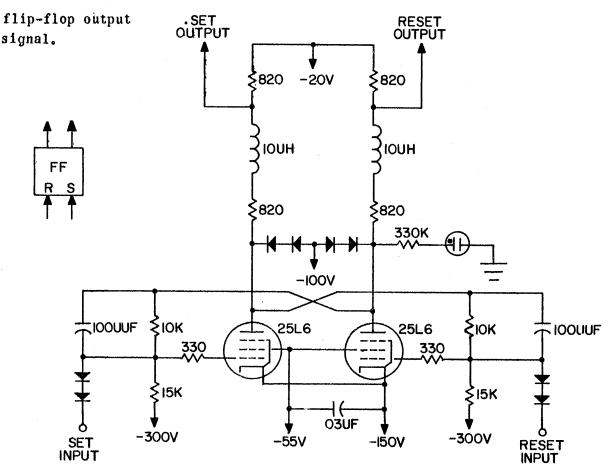

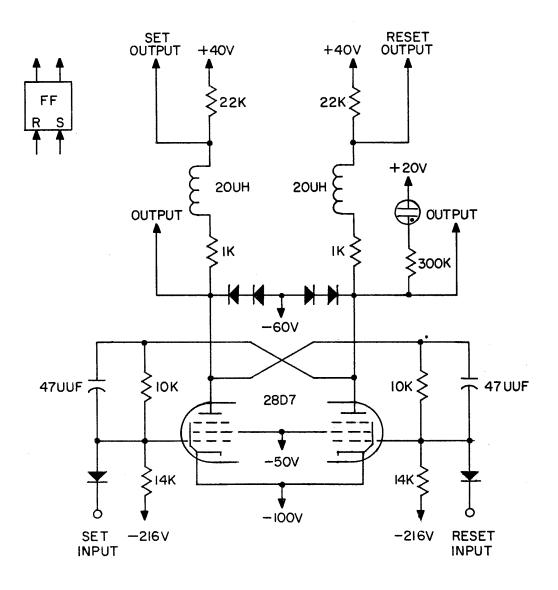

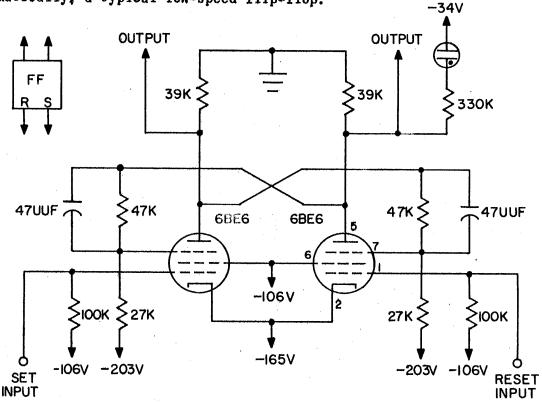

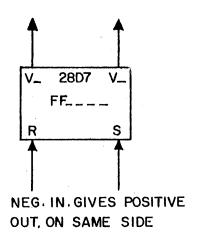

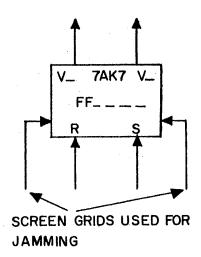

| 3-7.          | Typical High Speed Flip-Flop Circuit, .08 µsec                | <b>7</b> 3 |

| 3-8.          | Typical Medium Speed Flip-Flop Circuit, 2-4 μsec              | 74         |

| 3-9.          | Typical Low Speed Flip-Flop Circuit, 20 µsec                  | <b>7</b> 5 |

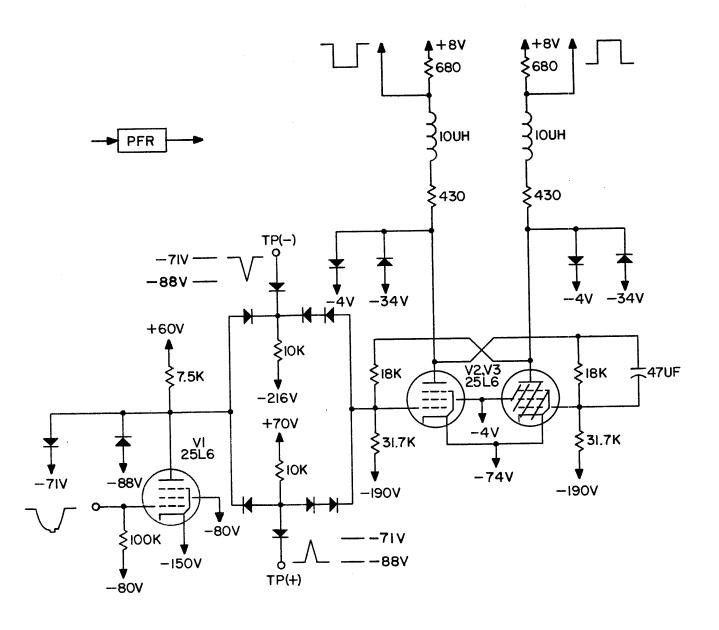

| 3-10.         | Schematic Diagram, Typical Pulse Former                       | 76         |

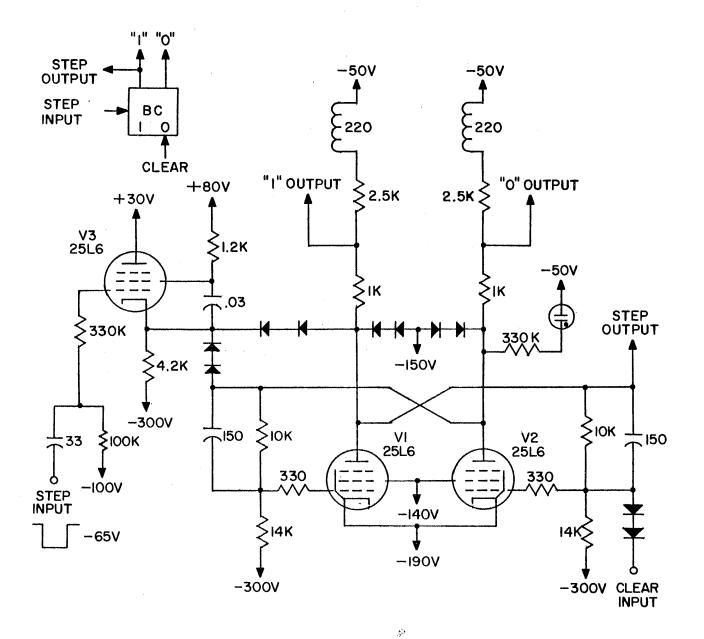

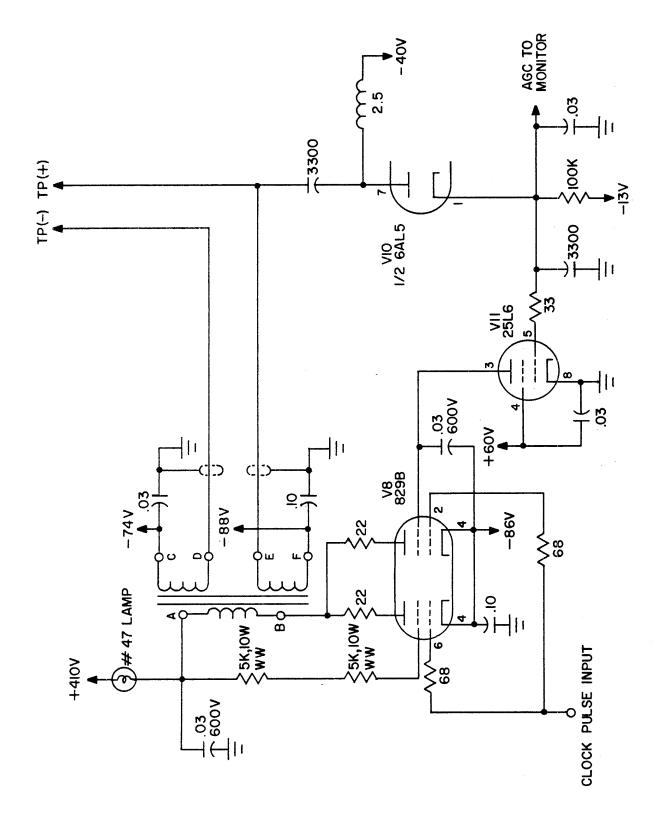

| 3-11.         | Schematic Diagram, Binary Counter                             | 79         |

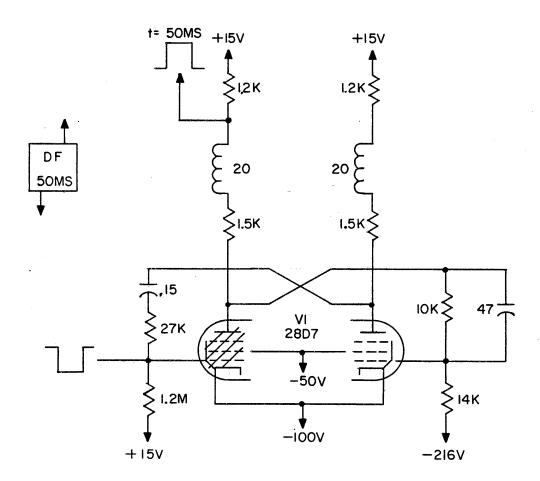

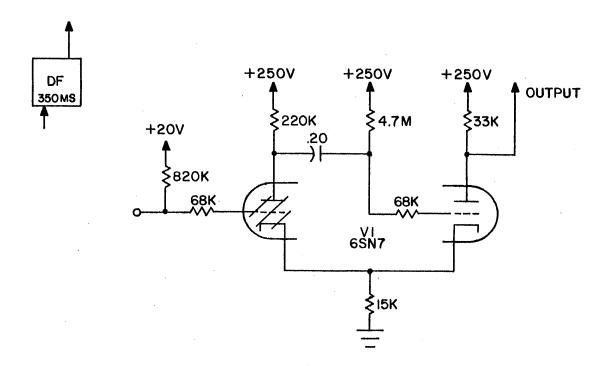

| 3-12.         | Schematic Diagram, Delay Flop - 50 Millisecond Delay Period . | 80         |

| 3-13.         | Schematic Diagram, Delay Flop - 350 Millisecond Delay Period. | 81         |

| 3-14.         | Schematic Diagram, Typical Thyraflop, 10 Millisecond Delay    |            |

| 0.45          | Period                                                        | 82         |

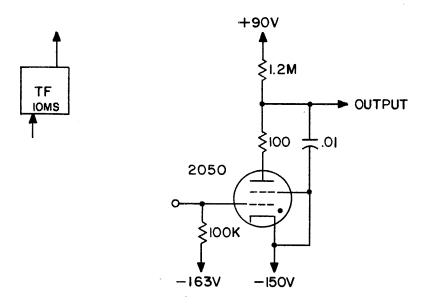

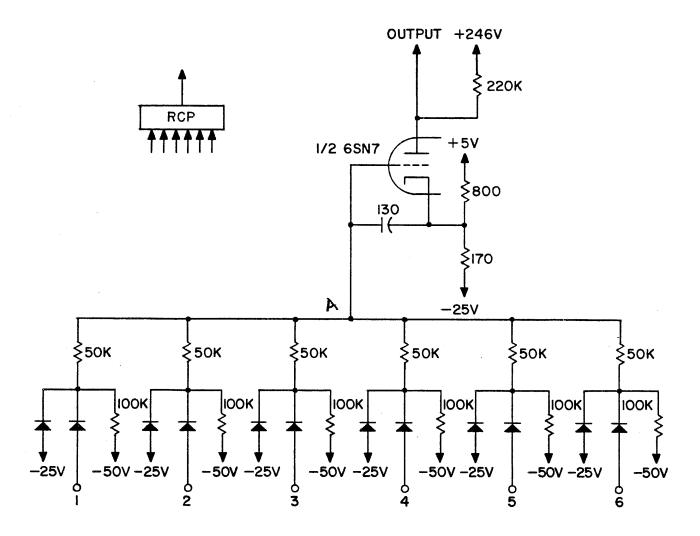

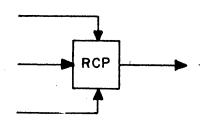

| 3~15.         | Schematic Diagram, Typical RCP                                | 84         |

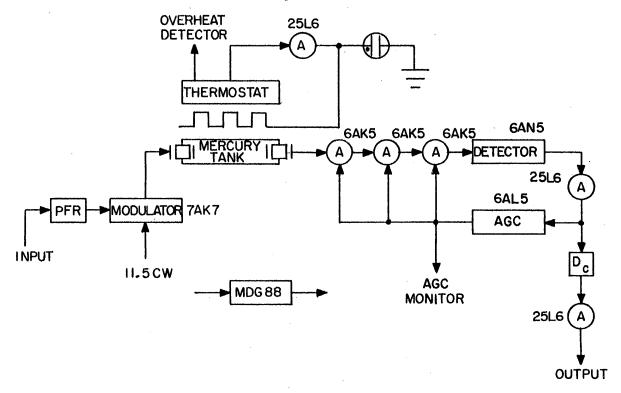

| 3-16.         | Short Mercury Tank Delay Group                                | 85         |

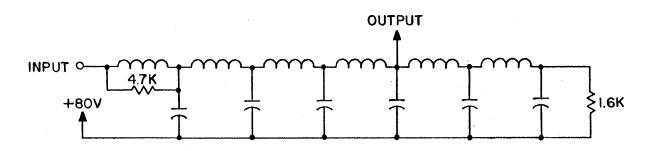

| 3-17.         | Electrical Delay Line                                         | 87         |

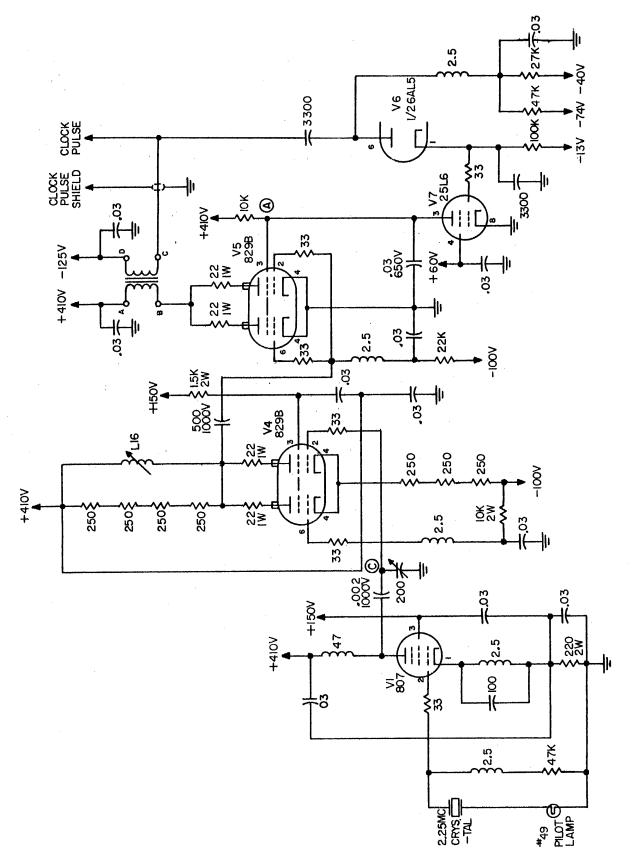

| 3-18.         | Schematic Diagram, Timing Pulse Generator                     | 89         |

| 3-19.         | Schematic Diagram, Typical Clock Gate Driver                  | 90         |

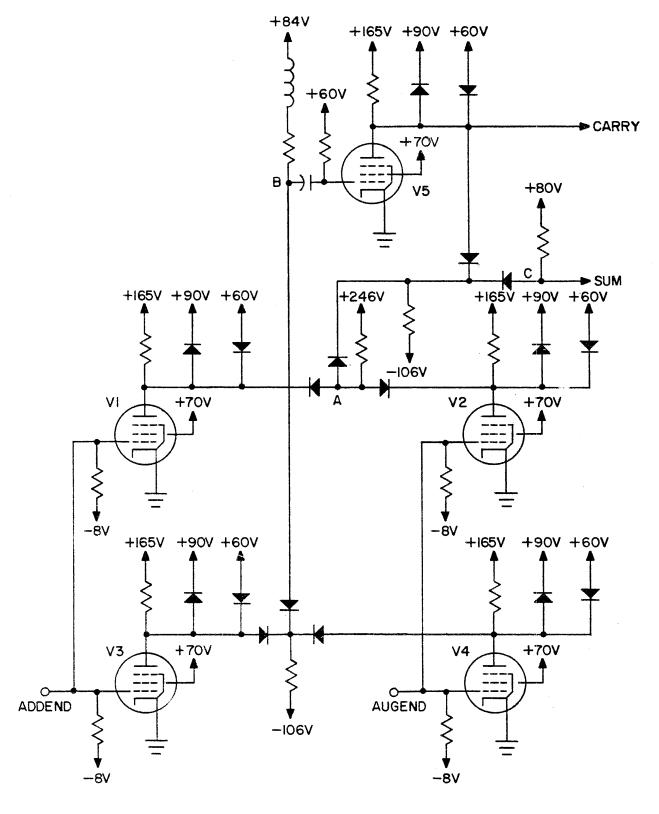

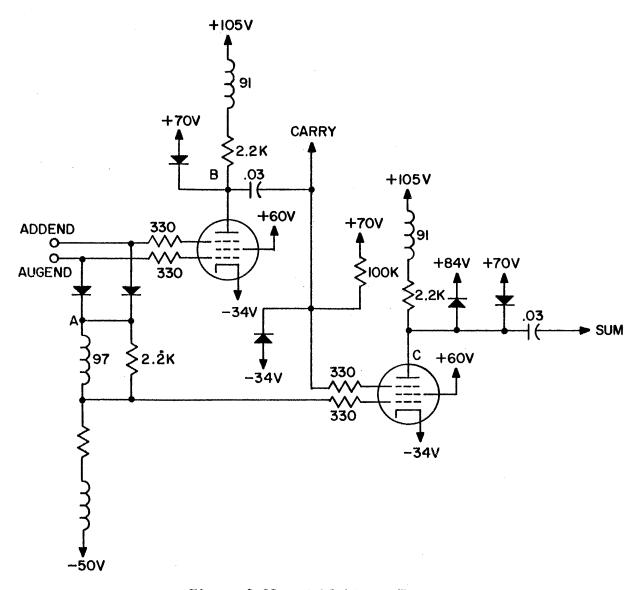

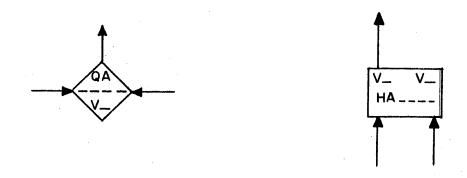

| 3-20.         | Typical Quarter Adder                                         | 92         |

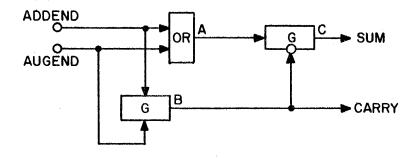

| 3-21.         | Typical Half Adder, Type I                                    | 94         |

| 3-22.         | Half Adder, Type II                                           | 95         |

| 3-23.         | Logical Diagram, Half Adder                                   | 95         |

# LIST OF ILLUSTRATIONS (Cont.)

| Figure            | <u>Title</u>                                                 | Page       |

|-------------------|--------------------------------------------------------------|------------|

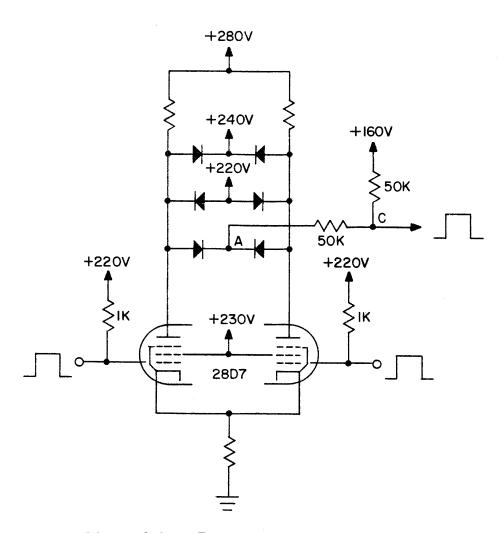

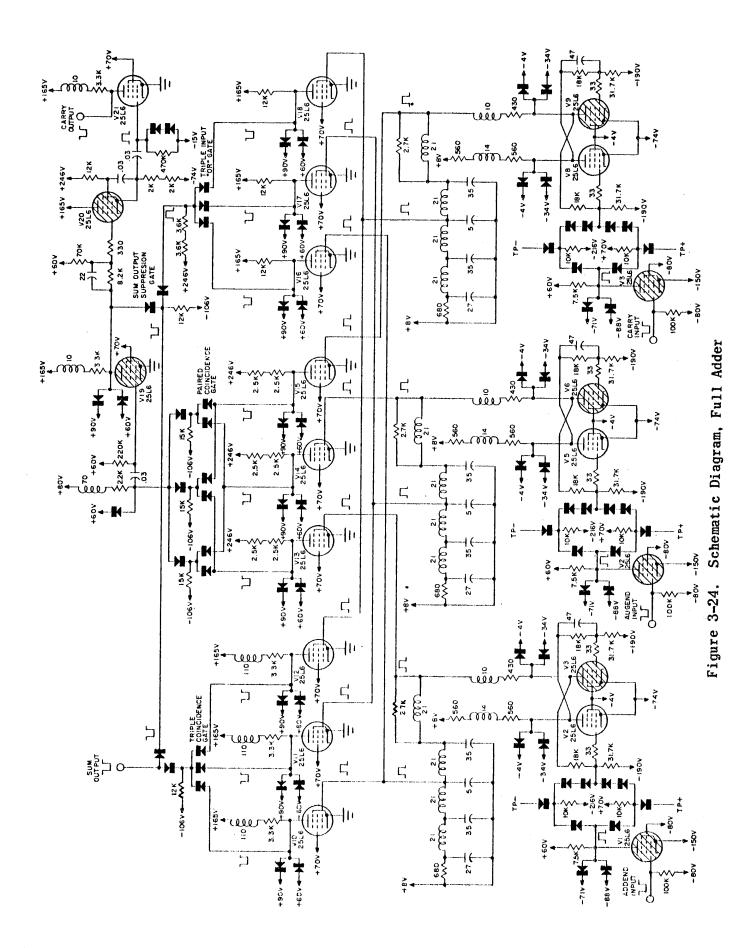

| 3-24.             | Schematic Diagram, Full Adder                                | 96         |

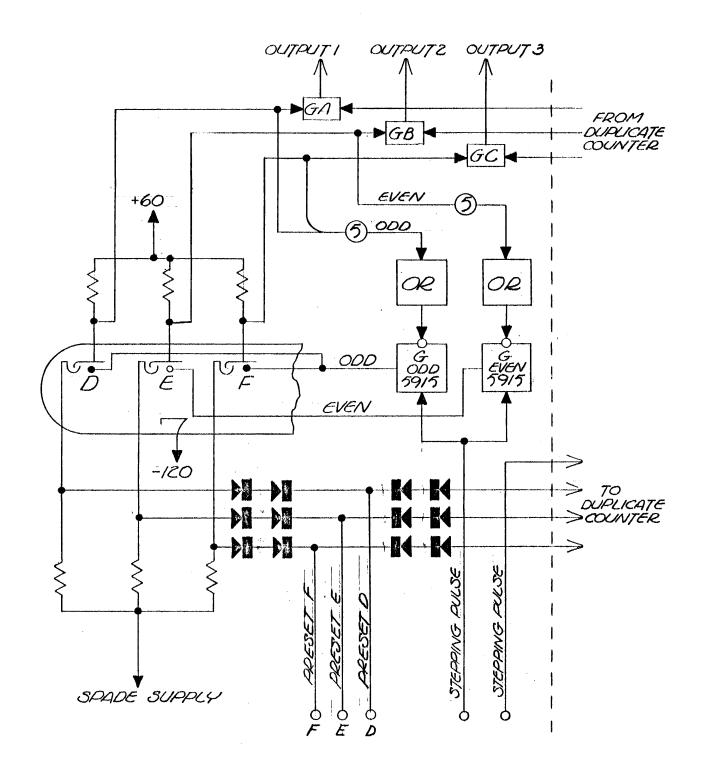

| 4-1.              | Magnetron Counter                                            | 107        |

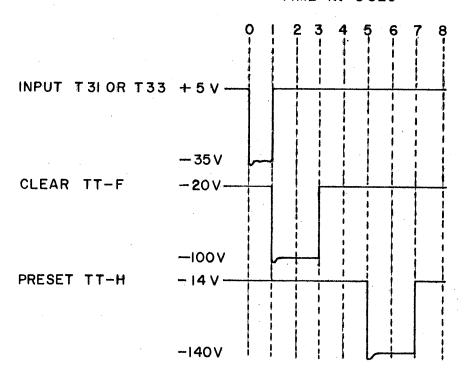

| 4-2.              | Clear and Preset Timing                                      | 109        |

| 4-3.              | No Address Error Circuit                                     | 115        |

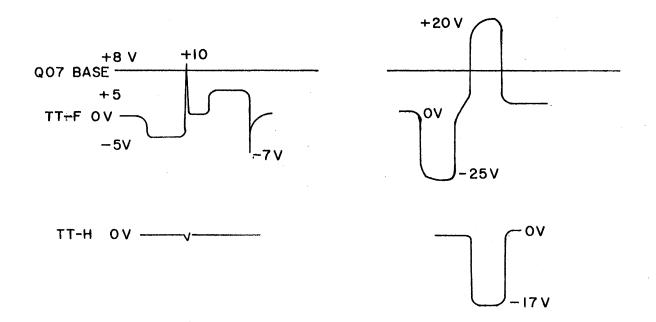

| 4-4.              | Pulse Former, Positive, Timing                               | 117        |

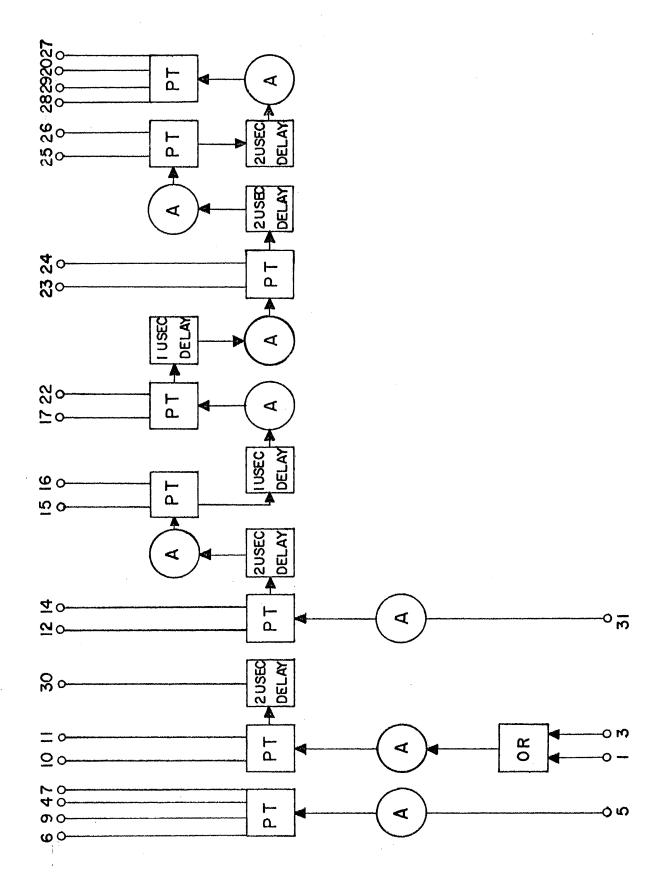

| <b>4</b> ~5.      | Staticizer-Serializer Gates (LSB and MSB Shown)              | 120        |

| 4-6.              | Sequencer                                                    | 123        |

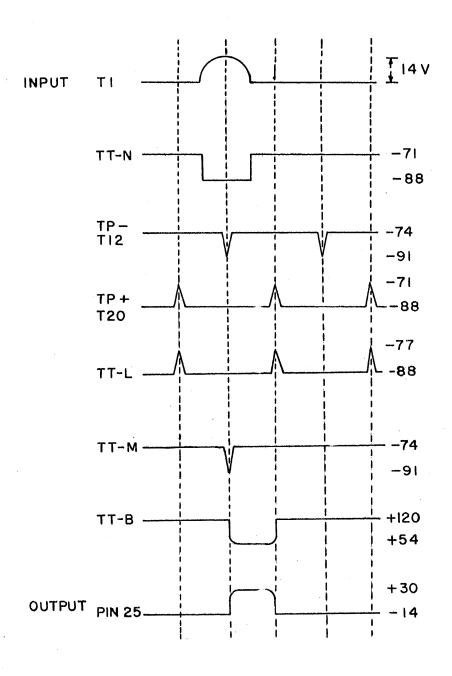

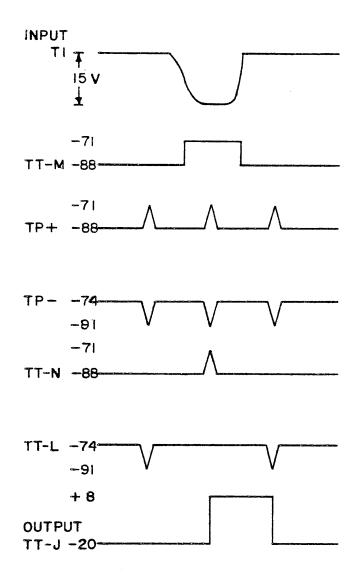

| 4 <b>~</b> 7.     | Pulse Former, Negative, Timing                               | 126        |

| <b>4-8.</b>       | OR Inverter                                                  | 127        |

| 4-9.              | Decode Enable                                                | 128        |

| 4-10.             | Magnetron Output Waveshape                                   | 131        |

| 4-11.             | AND Inverter                                                 | 133        |

| 4-12.             | Magnetron Output Waveshape                                   | 134        |

| 4-13.             | Magnetron Output Waveshape                                   | 136        |

| 4-14.             | Cathode Follower                                             | 138<br>139 |

| 4-15.             | Cathode Follower                                             | 141        |

| 4-16.             | Translator Diverter                                          | 141        |

| <b>4</b> →17.     | Buffer Diverter                                              | 146        |

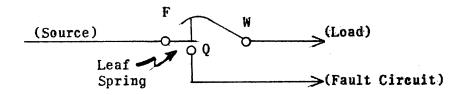

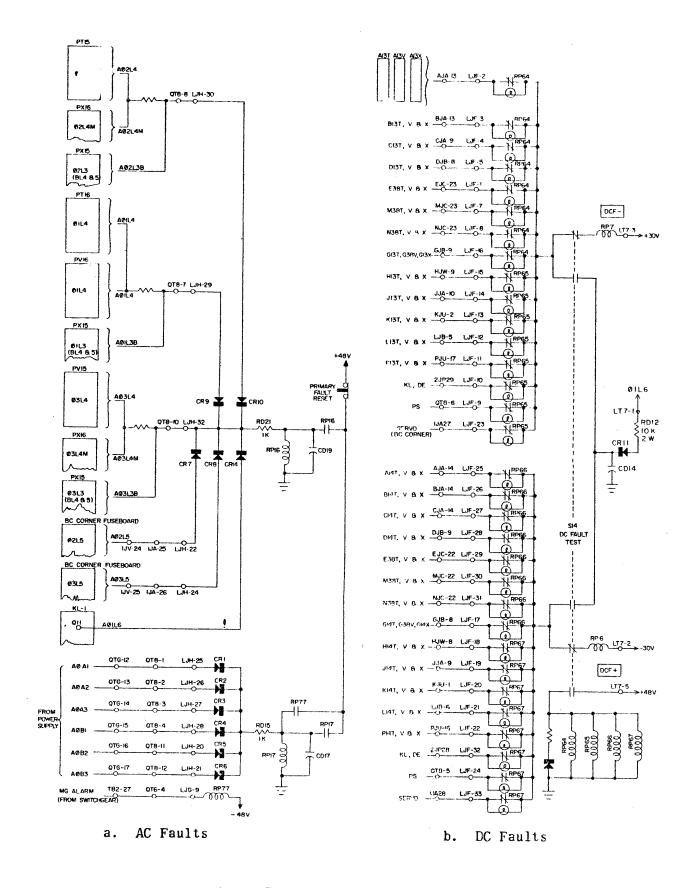

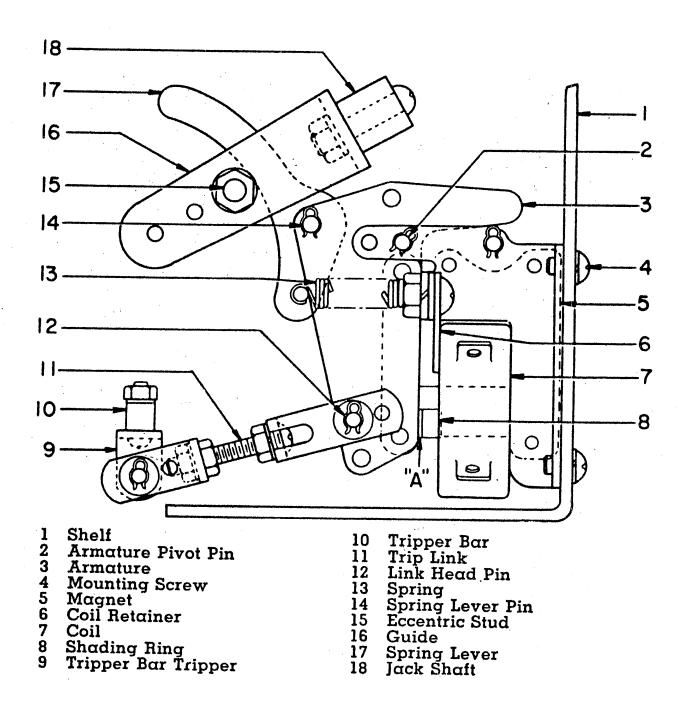

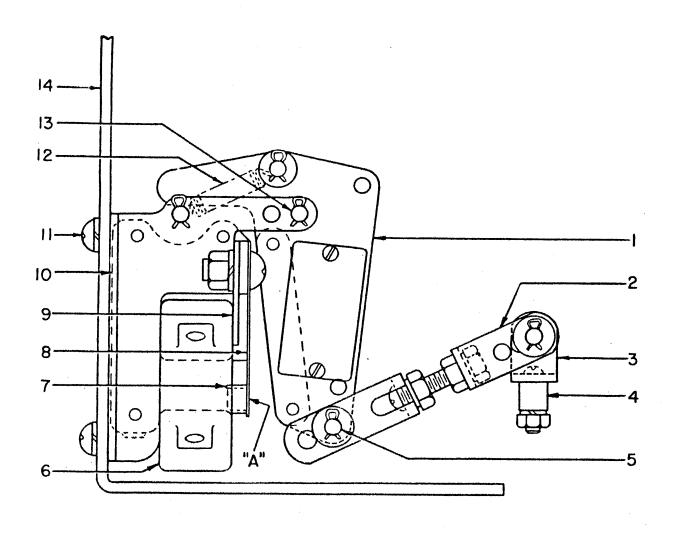

| 5 <b>-</b> 1.     | Grasshopper Fuse                                             | 144        |

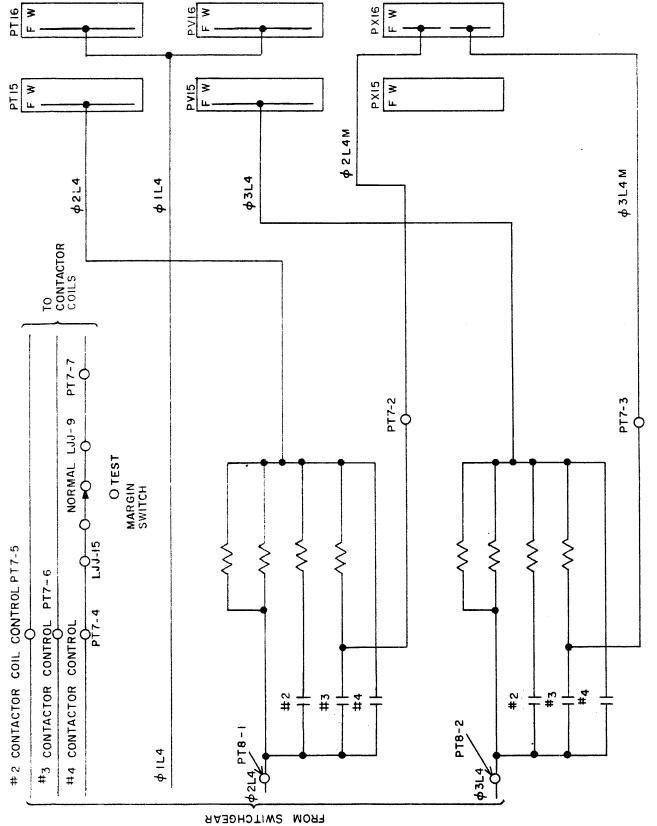

| 5 <b>-2</b> .     | Fault Circuits                                               | 146        |

| 5 <del>-</del> 3. | Protective Rectifier Interlock Circuit                       | 149        |

| 5 <del>-4</del> . | Door and Fuse Cover Interlock Circuit                        | 151        |

| 5 <del></del> 5.  | Bay Overheat and Hi Temp Circuits                            | 153        |

| 0-0               | bdy overhede and hi remp offedere \$ 6 6 6 6 6 6 6 6 6 6 6 6 |            |

| 6-1.              | The Supervisory Control Console                              | 155        |

| 6-2.              | Supervisory Control Panel, Rear View                         | <b>I57</b> |

| 6-3.              | Supervisory Control Panel, Mount, Rear View                  | 158        |

|                   |                                                              | 7- / · pt  |

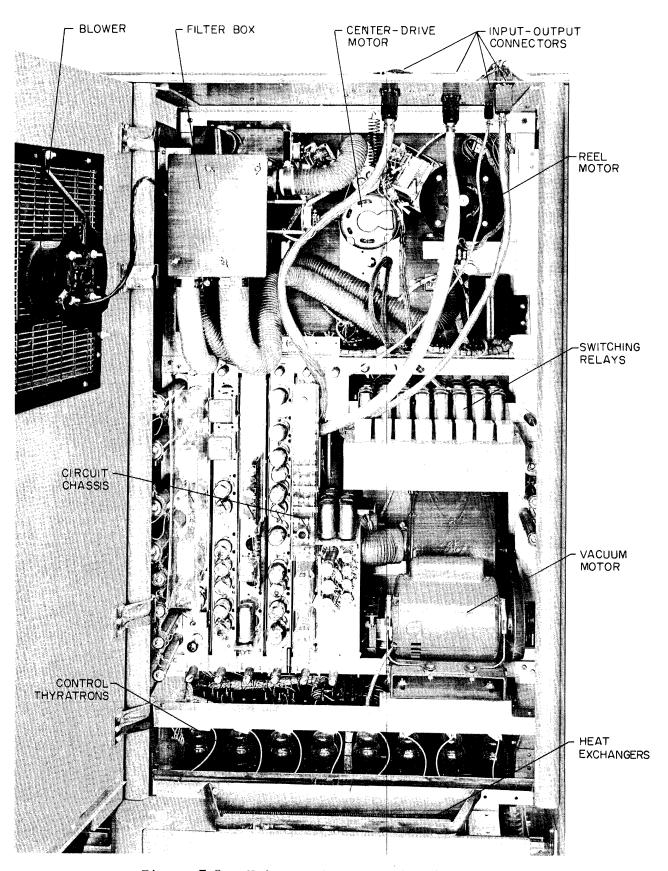

| 7-1.              | Uniservo II, Front View (Covers Removed)                     | 165        |

| 7⇔2.              | Uniservo II, Rear View (Door Open)                           | 166        |

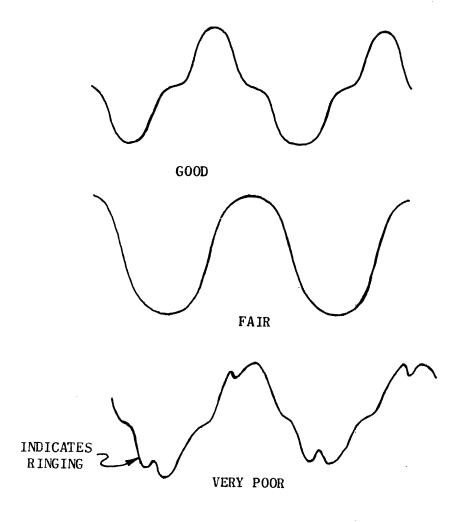

| <b>7-</b> 3.      | Write Voltage Waveforms                                      | 170<br>179 |

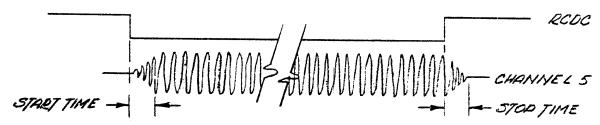

| 7-4.              | Tape Acceleration Test Patterns                              | 119        |

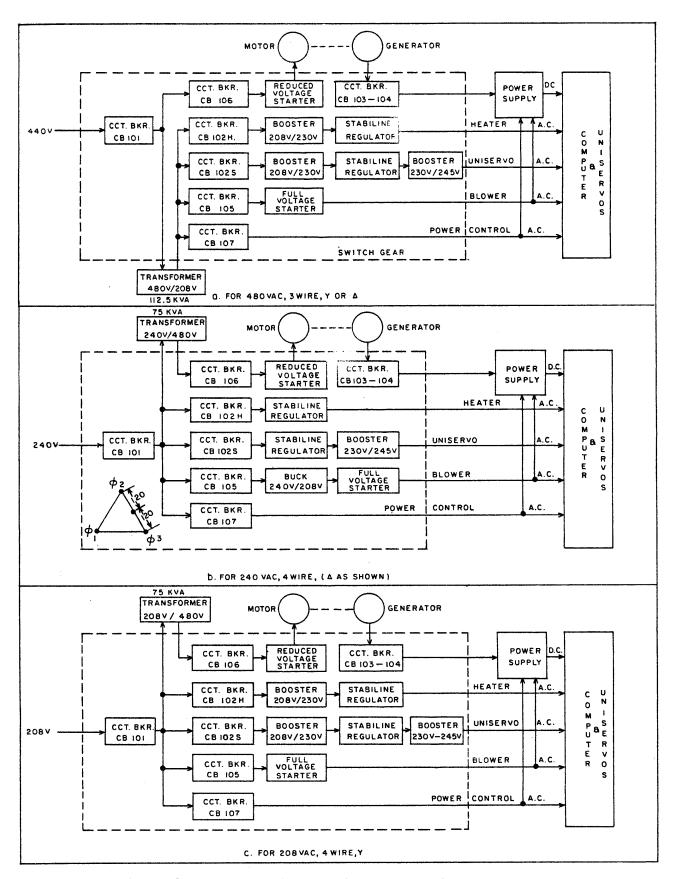

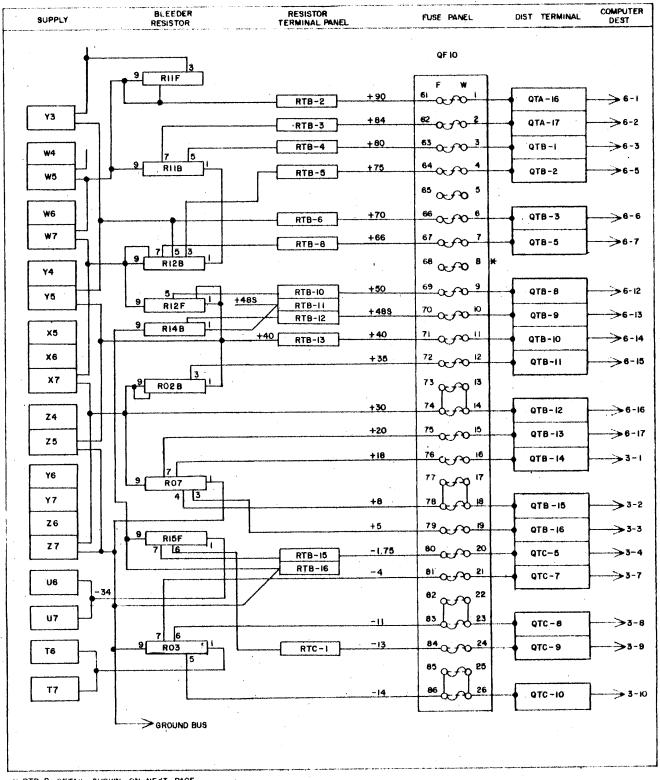

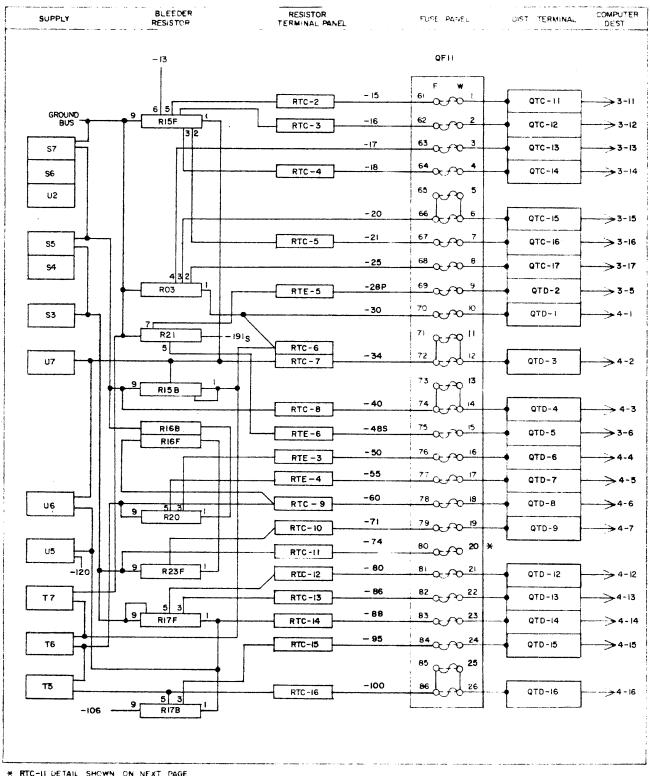

| 8-1.              | Power Distribution from Various Sources                      | 183        |

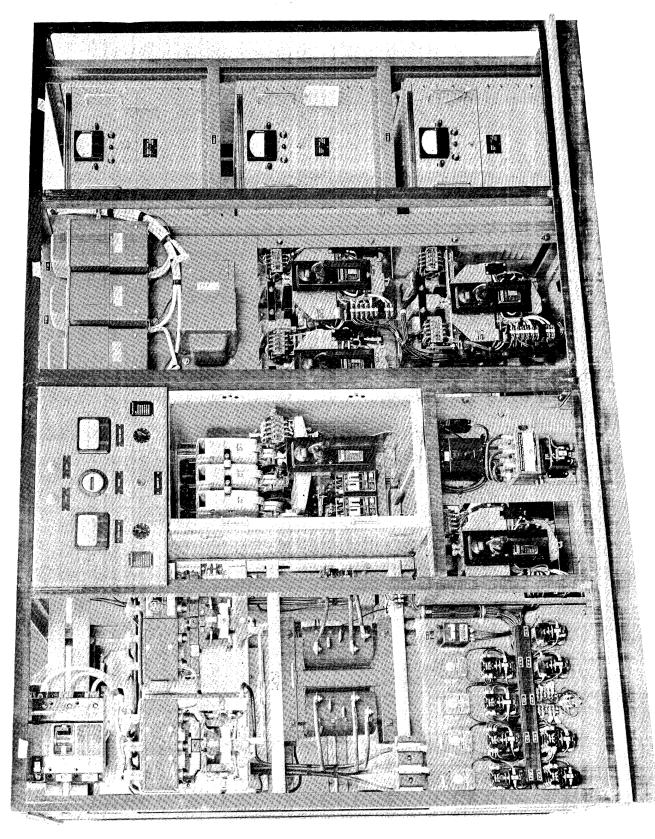

| 8 <b>→2</b> .     | Front View, Switchgear (Cover Removed)                       | 185        |

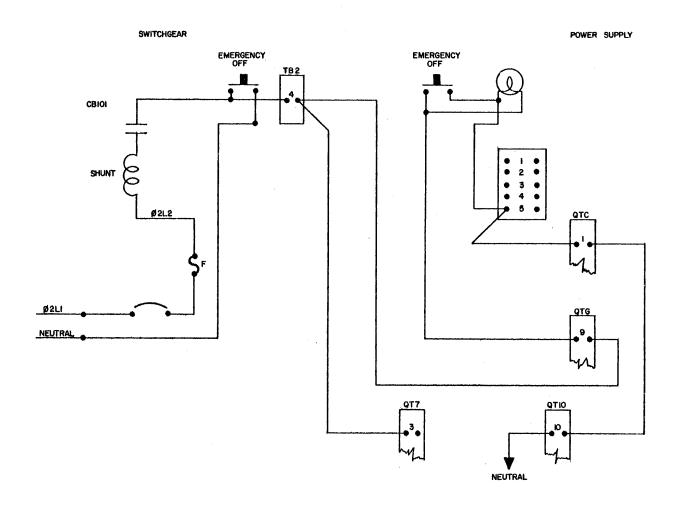

| 8 <b>-3.</b>      | Emergency-off Switch and Indicator Circuit                   | 187        |

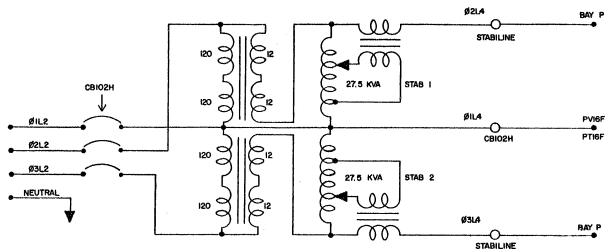

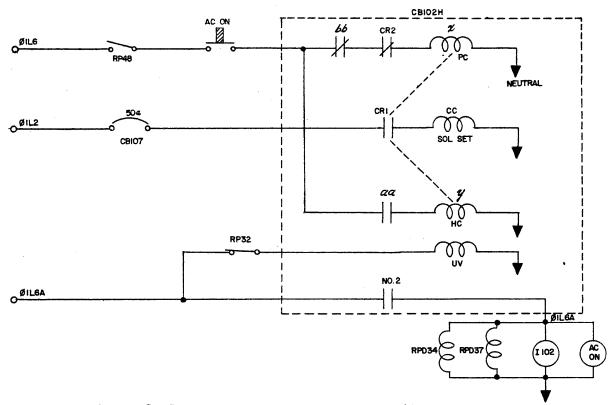

| 8-4.              | Heater AC CB102H Circuit (208V and 480V)                     | 189        |

| 8 <b>⇔</b> 5.     | Heater AC CB102H Circuit (240V)                              | 190        |

| 8-6.              | AC Voltmeter and Switching Circuit                           | 192        |

| 87.               | 400 Cycle AC Voltage Metering Circuit                        | 194        |

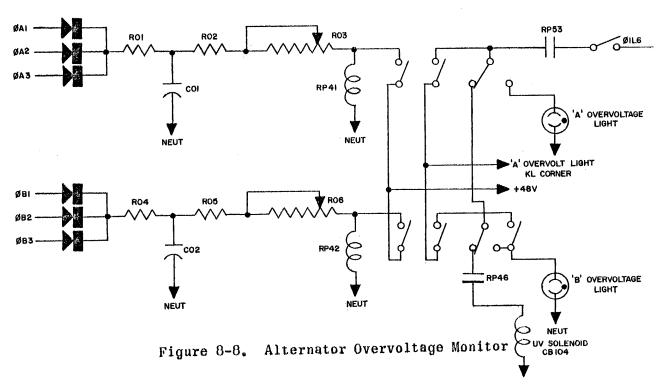

| 8-8.              | Alternator Overvoltage Monitor                               | 195        |

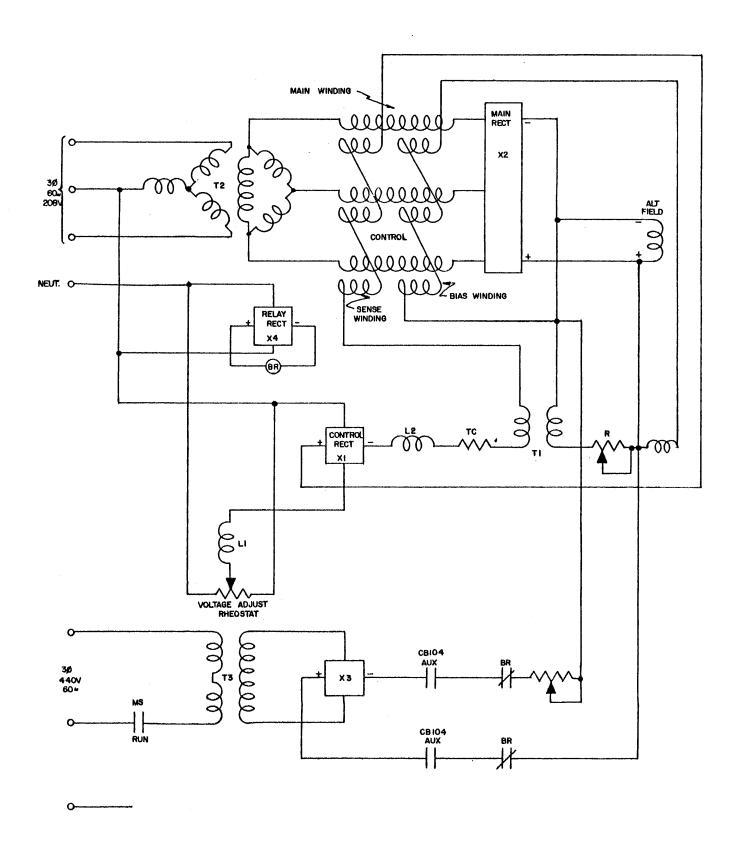

| 8-9.              | Magnetic Amplifier Regulator                                 | 197        |

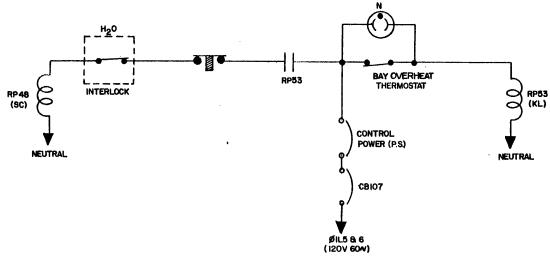

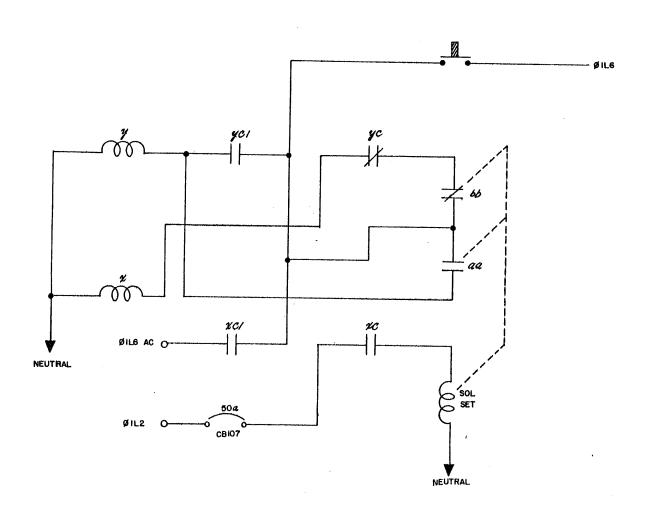

| 8-10.             | RP48-RP53 Solenoid Energizing Circuit                        | 201        |

| 8-11.             | I-T-E Type KA Breaker, Typical Wiring                        | 202        |

| 8-12.             | I-T-E Type KA Schematic Diagram                              | 203        |

|                   |                                                              |            |

# LIST OF ILLUSTRATIONS (Cont.)

# 8 (Cont.)

| Figure | <u>Title</u>                                                          | Page |

|--------|-----------------------------------------------------------------------|------|

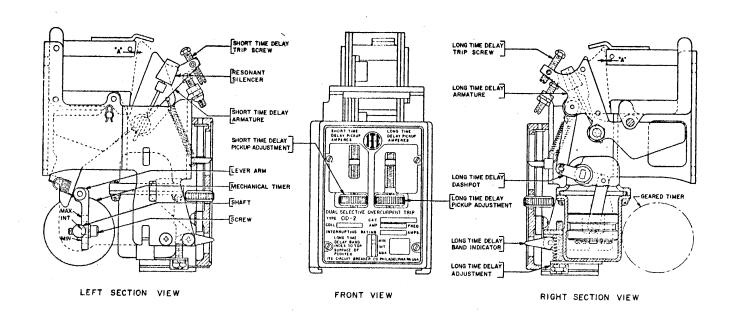

| 8-13.  | Undervoltage Trip Device for Type KA Circuit Breakers                 | 206  |

| 8-14.  | Shunt Trip Device for Type KA Circuit Breakers                        | 207  |

| 8-15.  | Overcurrent Trip Device for Type KA Circuit Breakers                  | 209  |

| 8-16.  | Typical G.E. AK-1-15-3 Schematic                                      | 211  |

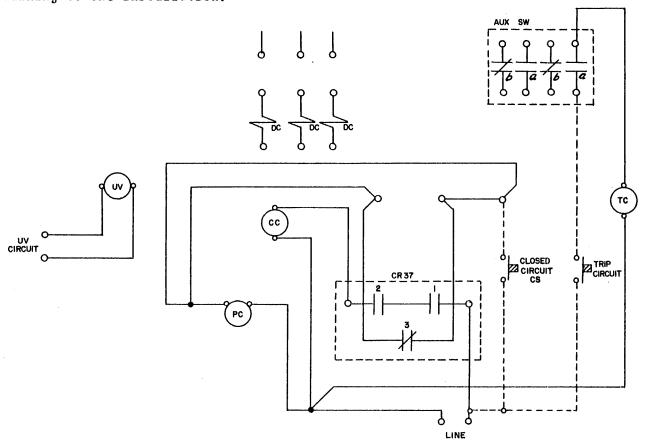

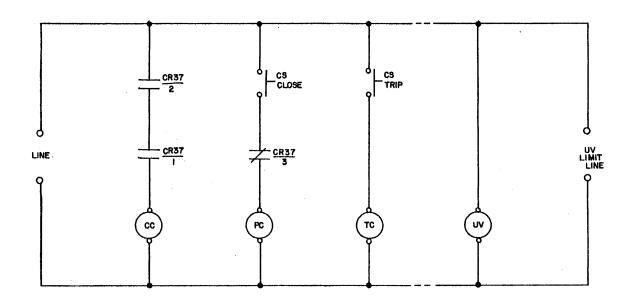

| 8-17.  | CB102H Closing Sequence (All contacts shown in non-actuated position) | 213  |

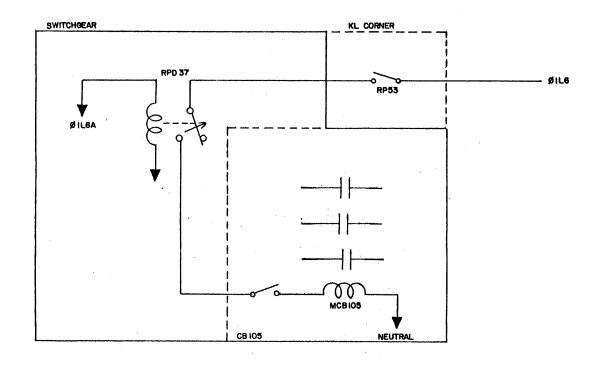

| 8-18.  | RPD 37 Contact Circuit                                                | 215  |

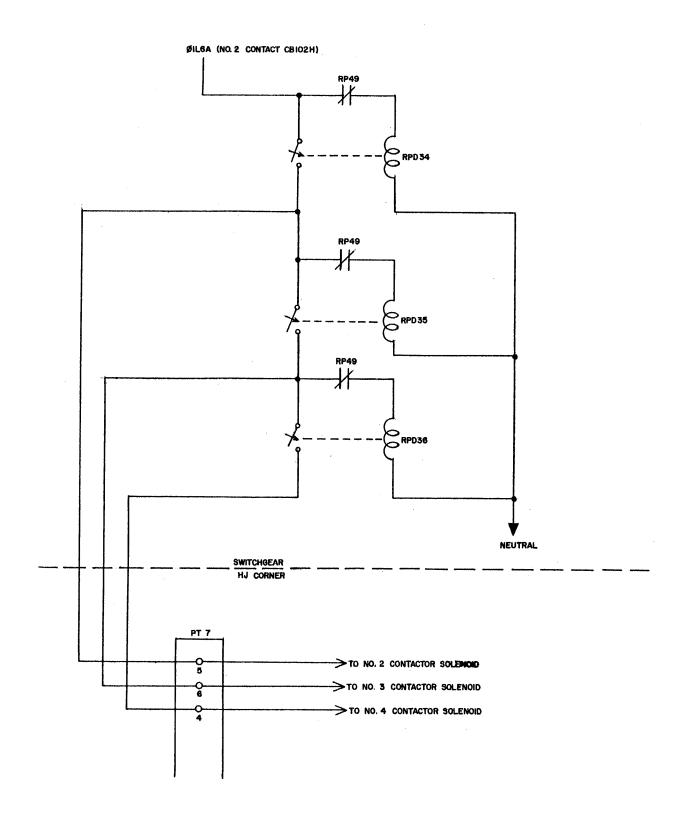

| 8-19.  | RPD 34-36 Solenoid and Contact Circuit                                | 216  |

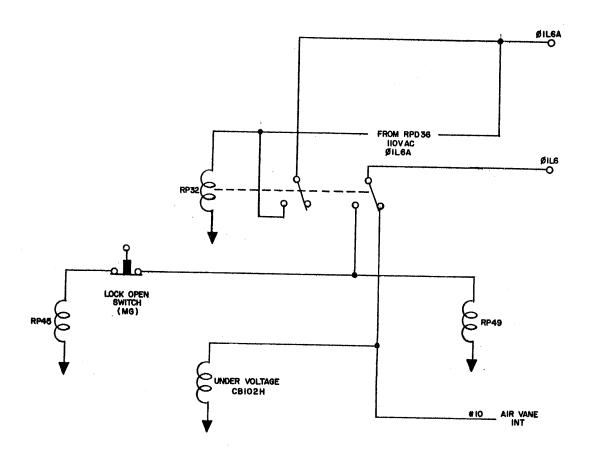

| 8-20.  | RP45, RP49 Actuating Circuit                                          | 218  |

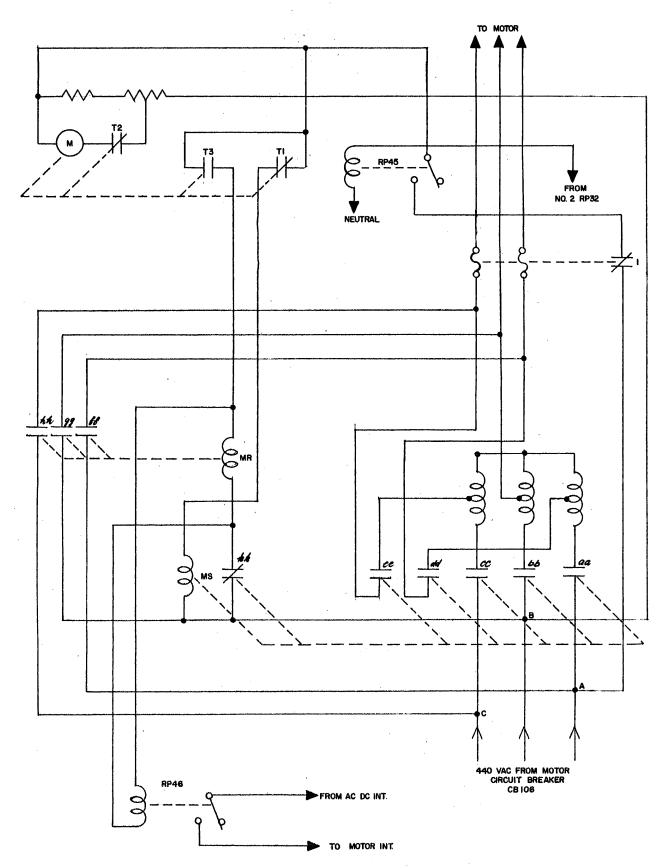

| 8-21.  | 75 HP Motor Starter Circuit                                           | 219  |

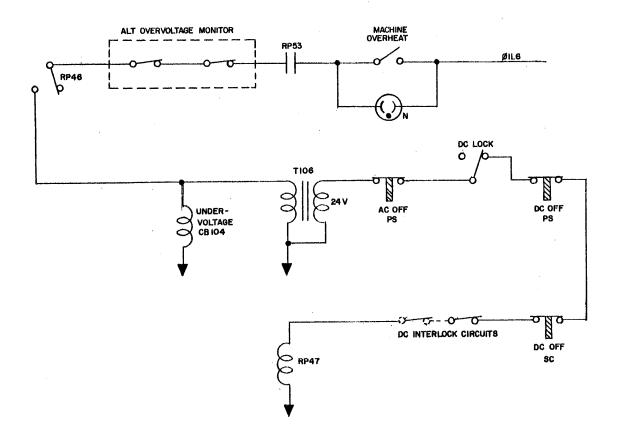

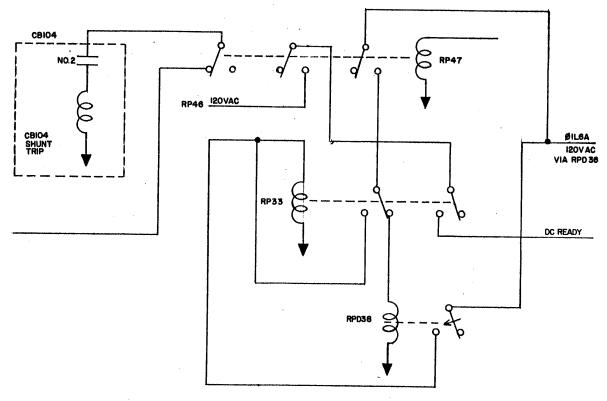

| 8-22.  | RP46 Contact Circuit - RP47 Energizing                                | 221  |

| 8-23.  | RP47-RP33-RPD38 Sequence                                              | 223  |

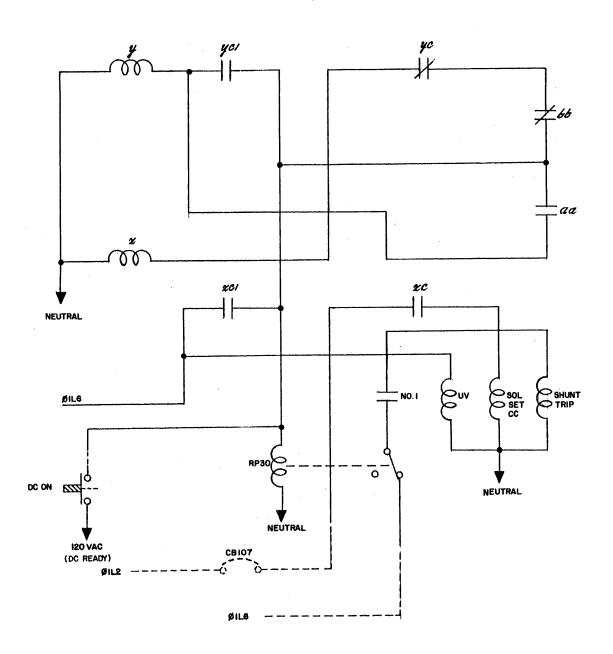

| 8-24.  | CB103 Actuating Circuits                                              | 225  |

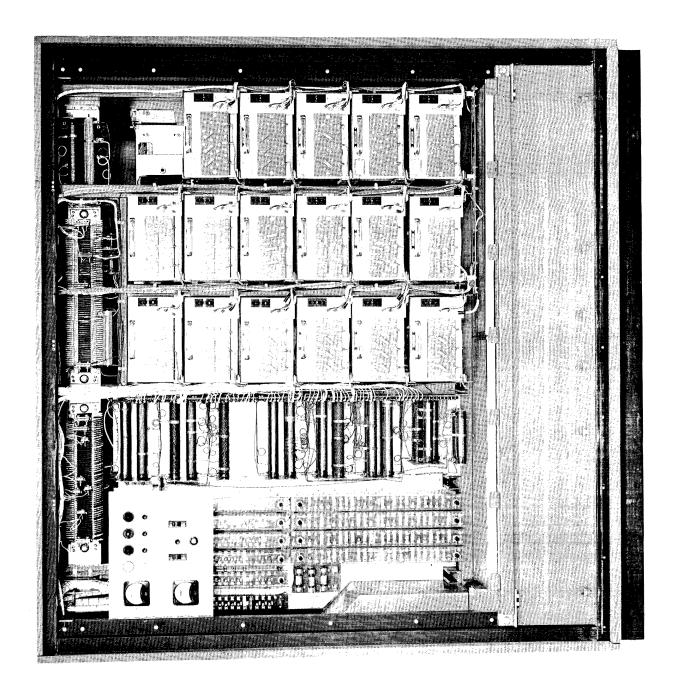

| 8-25.  | Power Supply, Front View (Cover Removed)                              | 229  |

| 8-26.  | Power Supply, Back View (Cover Removed)                               | 230  |

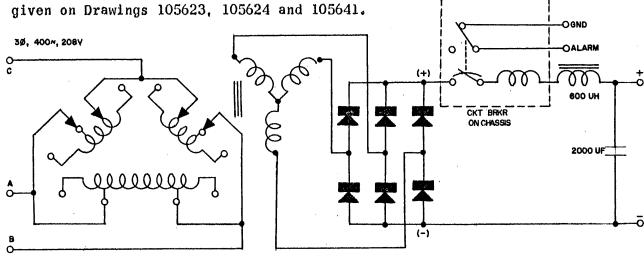

| 8-27.  | Schematic of Power Supply Chassis                                     | 233  |

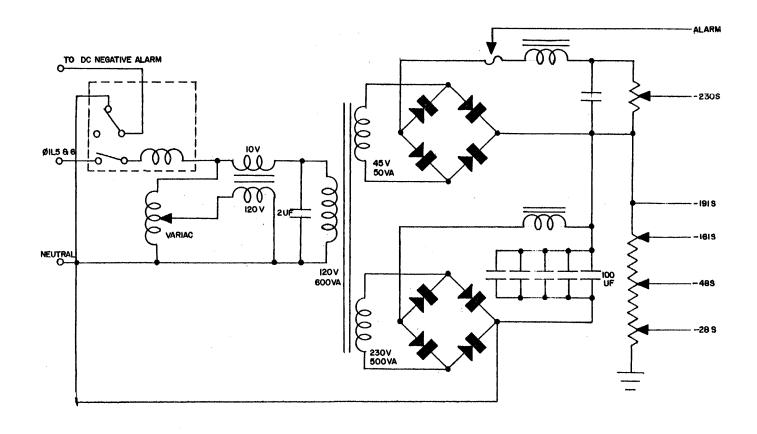

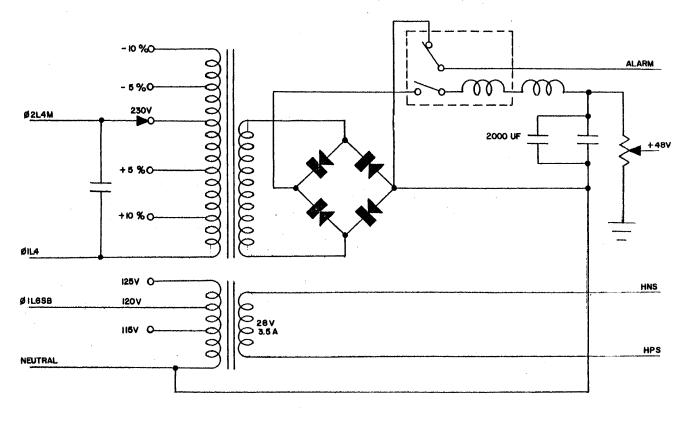

| 8-28.  | Standby Power Supply, Chassis Z2                                      | 235  |

| 8-29.  | Standby Power Supply, Chassis Z3                                      | 235  |

| 8-30.  | Positive and Negative DC Alarm Circuit                                | 238  |

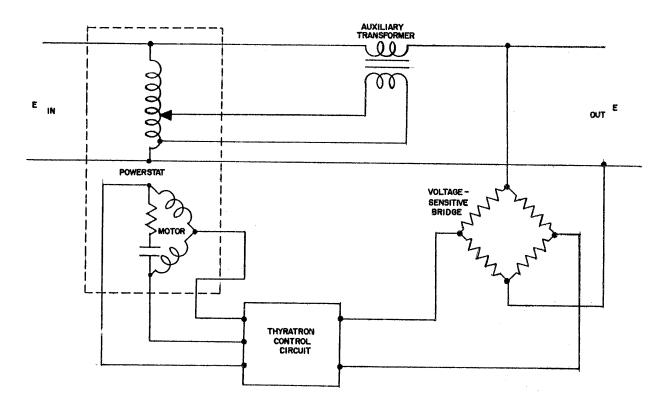

| 8-31.  | Simplified Schematic - Stabiline Type EM                              | 254  |

| 8-32.  | Motor - Generator Set, Back View                                      | 257  |

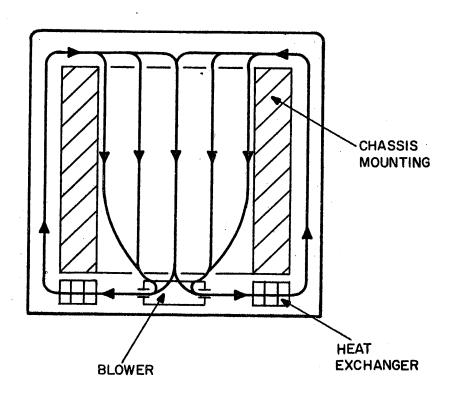

| 9-1.   | Univac II Closed Air Cooling System                                   | 262  |

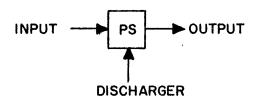

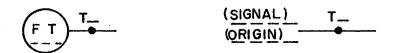

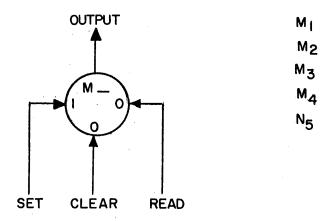

| 10-1.  | Basic Schematic Diagram Format                                        | 264  |

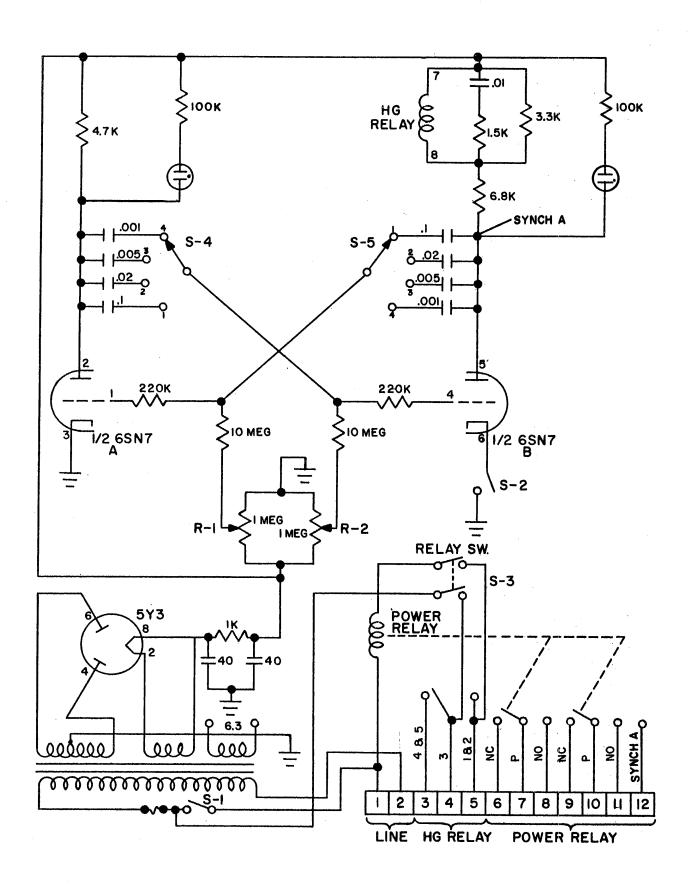

| C-1.   | Maintenance Multivibrator                                             | C-2  |

| D-1.   | Location of Control Helipots and Their Associated Bias                |      |

|        | Test Points                                                           | D-3  |

| D-2.   | Sense Amplifier Input of a DPC Chassis                                | D-4  |

| D-3.   | Control Panel, 53/54D Preamplifier                                    | D-5  |

| D-4.   | Memory Margin Test Data Recording Sheet                               | D-7  |

| D-5.   | Typical Example, Inhibit Current vs. Inhibit Control Bias.            | D-9  |

| D-6.   | Typical Example, Shmoo Diagram                                        | D-11 |

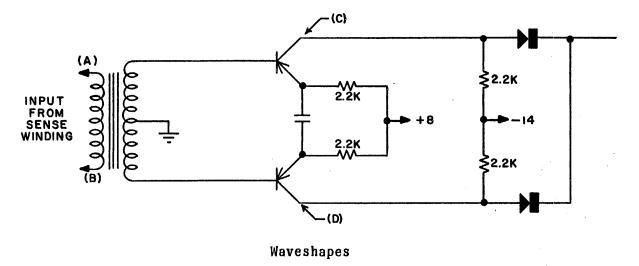

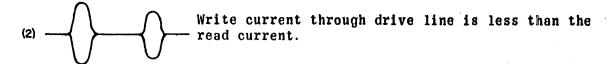

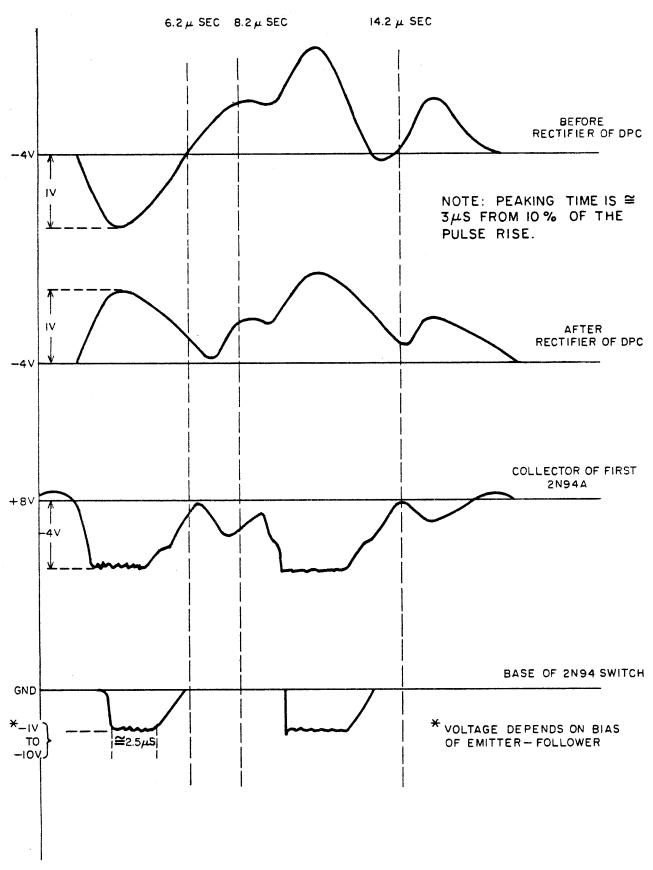

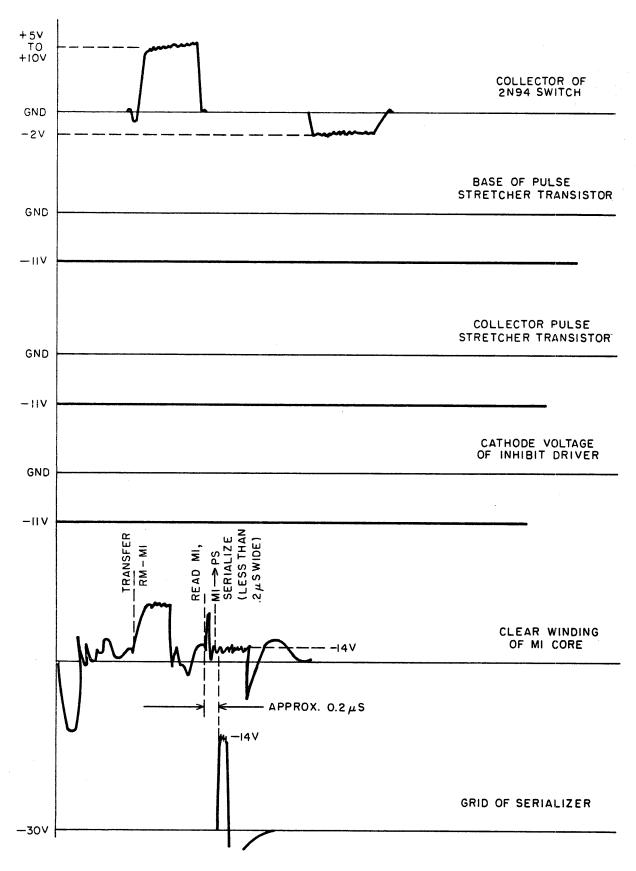

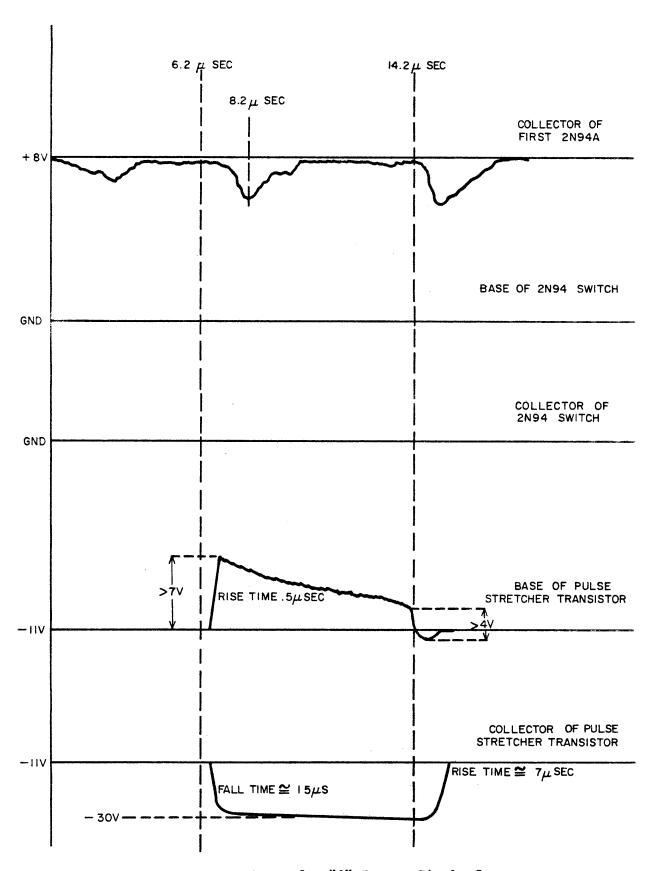

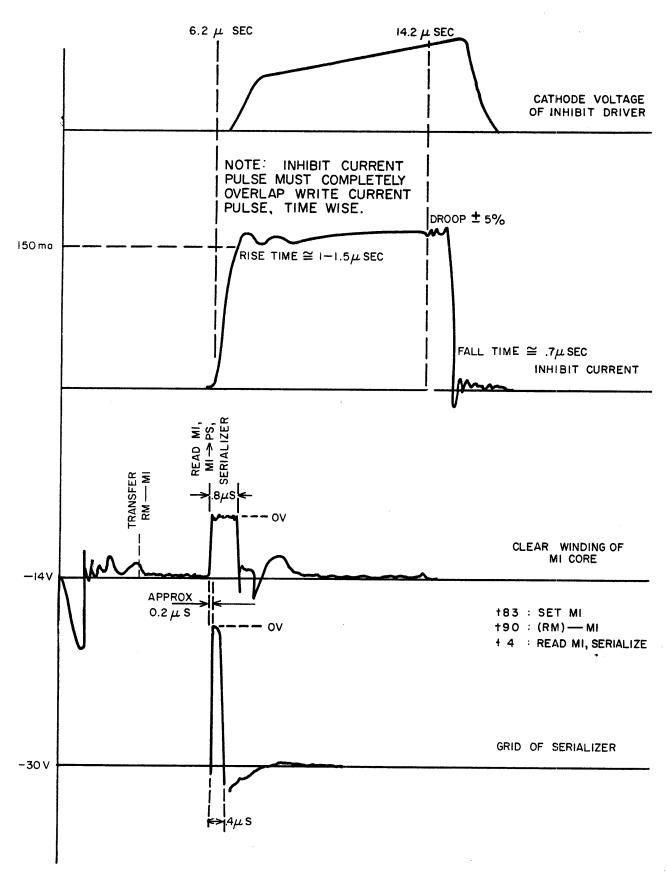

| D-7.   | Wave Shapes, Line Driver Chassis                                      | D-15 |

| D-8.   | Wave Shapes, Line Driver Chassis (continued)                          | D-16 |

| D-9.   | Readout of a "1" From a Single Core                                   | D-17 |

| D-10.  | Readout of a "1" From a Single Core (continued)                       | D-18 |

| D-11.  | Readout of a "O" From a Single Core                                   | D-19 |

| D-12.  | Readout of a "O" From a Single Core (continued)                       | D-20 |

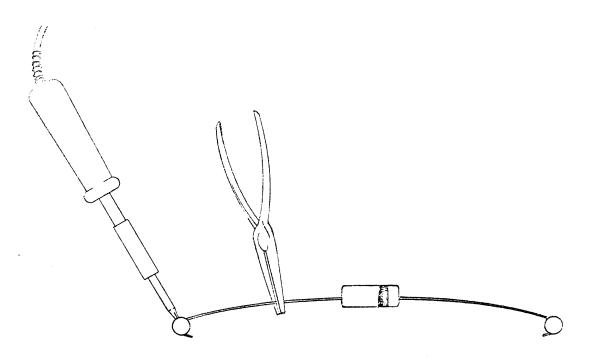

|        | nd E-2. Mounting Diodes                                               | E-2  |

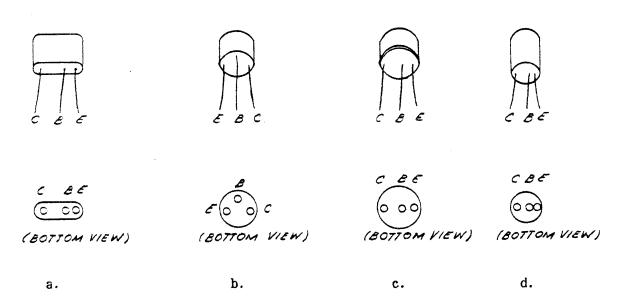

| E-3.   | Transistor Lead Identification                                        | E-5  |

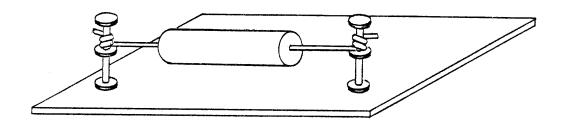

| E-4.   | Attaching Leads to Stud Terminals                                     | E-7  |

#### LIST OF ILLUSTRATIONS (Cont.)

| <u>Figure</u> | <u>Title</u>                             | Page |

|---------------|------------------------------------------|------|

| F-2.          | Front View of Transformer Terminal Board | F-3  |

|               | Positive Section Adjustments             |      |

#### LIST OF TABLES

| <u>Table</u> | <u>Title</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2-1.         | The state of the s | 5    |

| 2⇔2.         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12   |

| ∠⇔J.         | Section Edge Connections; Bays E. M. N and GV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19   |

| 2-4.         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25   |

| 2-5.         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37   |

| 2-6.         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 42   |

| 2-7.         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58   |

| 2-8.         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|              | Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59   |

| 2-9.         | Miscellaneous Components of Central Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63   |

| 4-1.         | Printed-Circuit Chassis Positions, Types, Totals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 102  |

| 6-1.         | Supervisory Control Mounted Relays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 159  |

| 8-1.         | Power Supply Primary Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 239  |

| 8-2.         | Power Supply Secondary Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 245  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| L-1.         | Diode Replacement Standards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | L-3  |

#### 1. GENERAL

An installation of the Univac II System consists of two major groups of equipment: the Central Computer group and the Input-Output Auxiliaries. The Central Computer group consists of the Central Computer, the Uniservos, the Power Supply, the Switchgear, the Motor-Generator Set, the Transformer, and the Supervisory Control Console with its Printer Dolly. All of these units are inter-related in function and cannot be treated separately. The Input Auxiliaries are those transcribing devices which receive information in the raw state (printed, written, or punched cards) and translate it into information on tape which is comprehensible to the Central Computer. The Output Auxiliaries receive information from the Central Computer, in the form of tape recordings, and translate it into printed matter or punched cards.

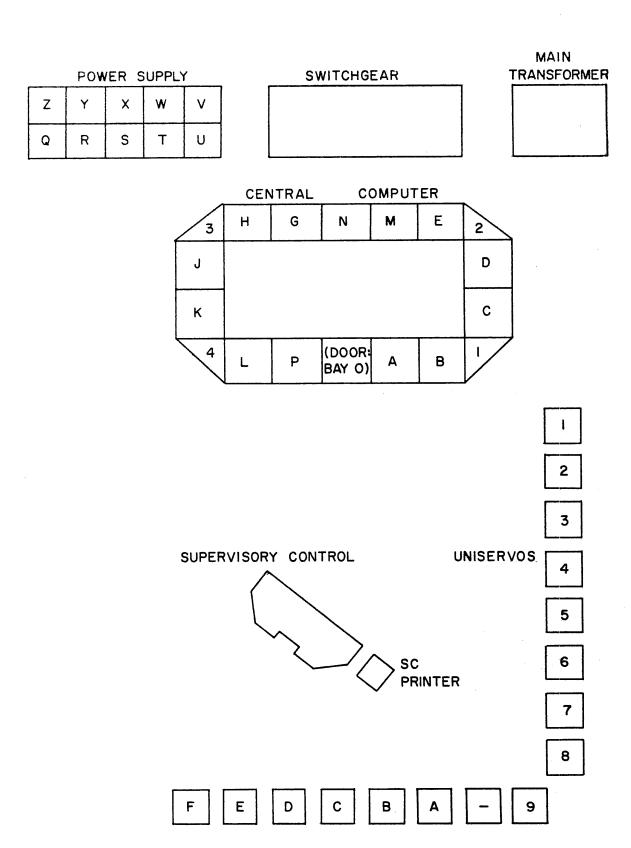

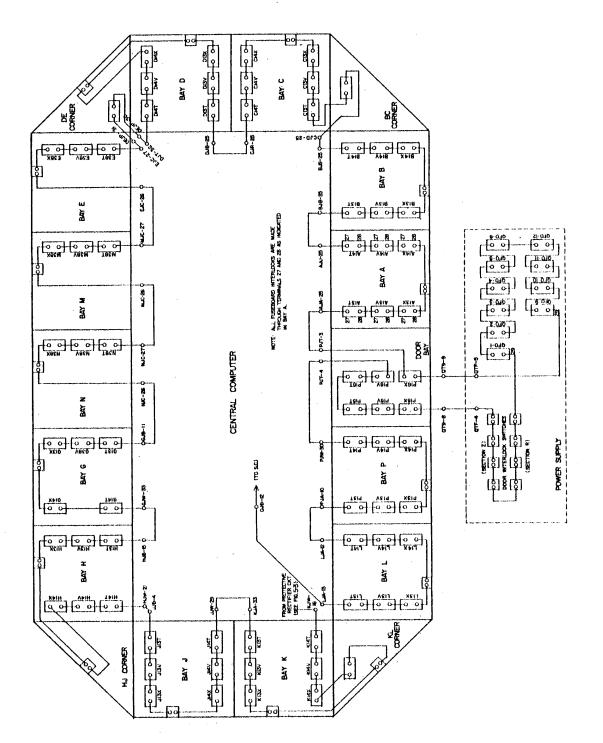

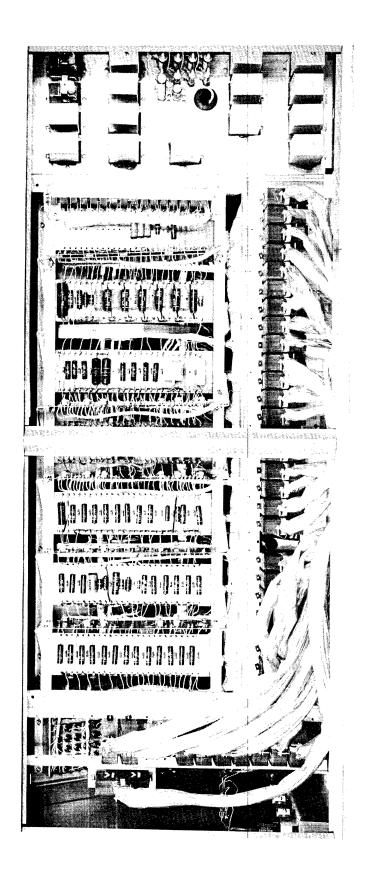

A typical Central Computer installation is shown in Figure 1-1. At the left are the three components of the Supervisory Control Console: the monitor oscilloscope, the control panel and keyboard, and the printer. At the rear is the Central Computer and at the right, lined up perpendicular to the length of the Central Computer, are the Uniservos. The Power Supply, which does not appear in the photograph, is behind the computer.

This manual includes a detailed physical description of the Central Computer group and an electrical description of the basic circuits. The remainder of the manual is devoted to maintenance and troubleshooting information.

(Continued on Page 3)

Figure 1-1. A Typical Central Computer Installation

#### (Continued from Page 1)

Maintenance information on the input-output auxiliaries are not given here, since they are covered in complete detail in the manuals for those equipments.

#### 2. PHYSICAL DESCRIPTION OF CENTRAL COMPUTER

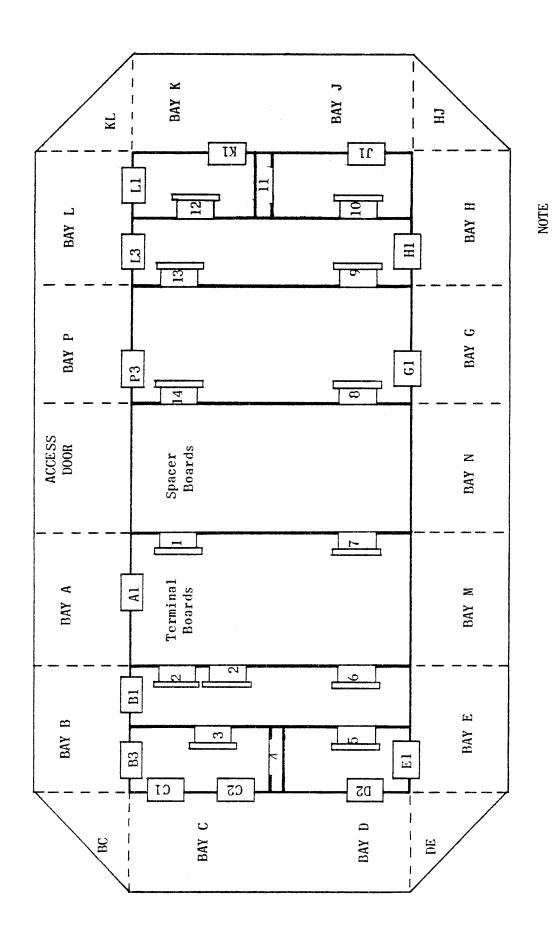

a. GENERAL. - The Central Computer group is composed of a number of modular units; this feature facilitates the location and replacement of components and the tracing of connections. The major modular unit is the "bay", of which there are a total of 28. The bays are assigned discrete alphabetic and numeric designations.

The larger bays of the Central Computer are divided into "sections". The sections of each bay are designated T, V and X, from top to bottom.

The smallest modular division of the Central Computer group is the "unit". Each section or bay is composed of a number of units, which are assigned alphabetical and numeric designations. A unit may be a chassis, a fuseboard, an indicator panel, or any externally-mounted component of the Central Computer group.

#### b. MODULAR BREAKDOWN

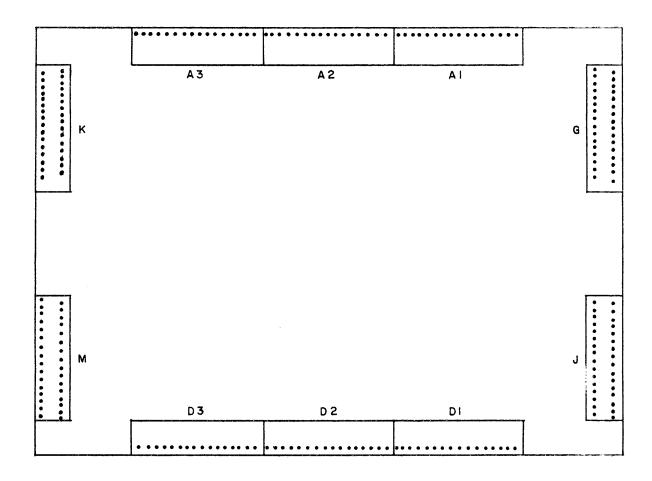

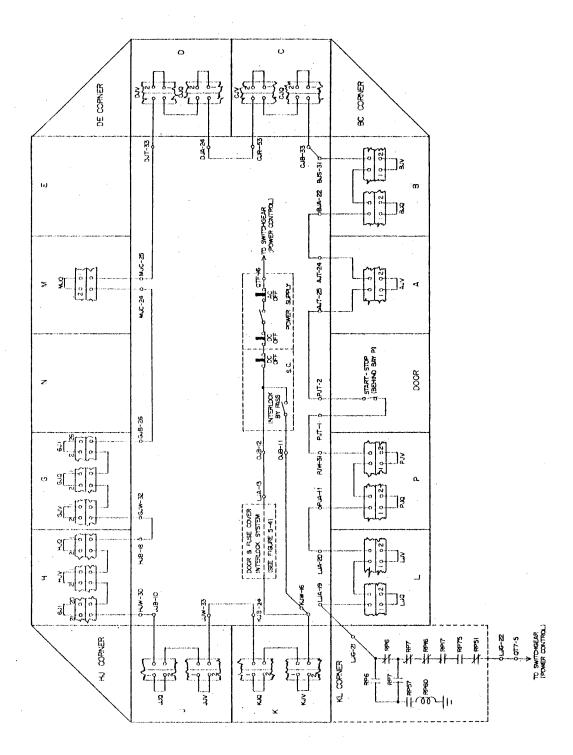

(1) BAYS. - The Central Computer is divided into 18 bays, as shown in Figure 2-1. Thirteen of these bays, designated A, B, C, D, E, M, N, G, H, J, K, L & P consist of the unit chassis mounted on their backboards. The remaining bays are designated as follows: bay 0 is the access door, bays 1, 2, 3 and 4 are the corners.

A list of all the bays of the Central Computer, and the principal circuits contained in each, is provided in Table 2-1.

#### (Continued on Page 6)

Figure 2-1. Bay Designations of Central Computer Group

TABLE 2-1

PRINCIPAL CIRCUITS IN EACH BAY OF CENTRAL COMPUTER

| Bay | Circuits                                                                                                  |

|-----|-----------------------------------------------------------------------------------------------------------|

| A   | Input and Output Circuits                                                                                 |

| В   | Function Table                                                                                            |

| С   | Function Table: Control Circuits                                                                          |

| D   | Static Register; Decorders                                                                                |

| E   | Register M Circuits                                                                                       |

| М   | Register M and Register O Circuits                                                                        |

| N   | Register M and Register I Circuits                                                                        |

| G   | HSB & HSB; X & X; Register I Circuits                                                                     |

| Н   | X & X; Cycling Unit                                                                                       |

| J   | L& L; F& F; A& A; Cycling Unit                                                                            |

| K   | A & A; AA & AA; Cycling Unit                                                                              |

| L   | AA & AA; Cycling Unit                                                                                     |

| P   | CP & CP; Cycling Unit                                                                                     |

| 0   | Access door                                                                                               |

| 1   | BC Box; FT Neons; Filament Transformers; Bypass Capacitors                                                |

| 2   | Filament Transformers; Bypass Capacitors                                                                  |

| 3   | Slow Heater Turn-on Relays; Bypass Capacitors                                                             |

| 4   | Filament Transformers; Fault Indicators; Maintenance<br>Switches; Power Control Relays; Bypass Capacitors |

#### (Continued from Page 3)

(2) SECTIONS. - The unit chassis bays of the Central Computer are each divided into three sections, designated T, V and X (from top to bottom). The three sections of bays A, B, C, D, H, J, K, L and P, and sections GT and GX, each provide mounting space for 12 conventional chassis, numbered from 1 to 12, and two fixed fuseboards, numbered 13 and 14. A front view of a typical section of this type is shown in Figure 2-2 (a). The three sections of bays E, M and N, and section GV, provide mounting space for 36 printed circuit chassis, numbered from 1 to 36, plus an indicator panel, numbered 37, and a fuseboard, numbered 38. A front view of a typical printed-circuit section is shown in Figure 2-2 (b).

The electrical connections to each section are made at the rear of the section and involve three types of wiring: power wiring, low-speed signal wiring, and high-speed signal wiring. The power wiring handles all a-c and d-c voltages from the Power Supply and Switchgear; the low-speed signal wiring transfers the slow rise-time signal voltages between the chassis, and the high-speed signal wiring transfers the fast rise-time signal voltages. The three types of wiring are described in detail in a later paragraph.

- (3) UNITS. The bays and sections of the Central Computer are composed of a large number of units which are mounted on the framework of the computer and connected by power and signal wiring. The principal unit of the Central Computer is the unit chassis; these chassis contain most of the circuitry of the computer and are of two types: conventional and printed-circuit.

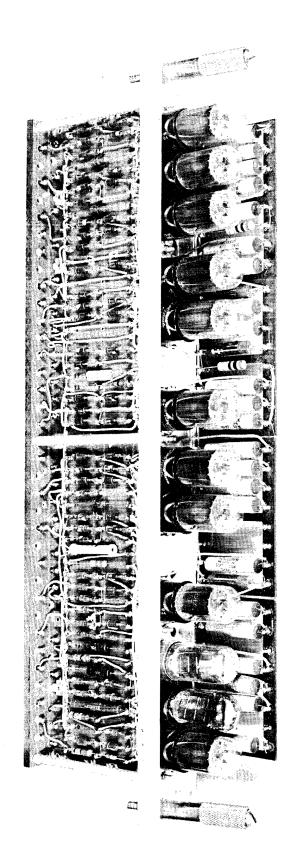

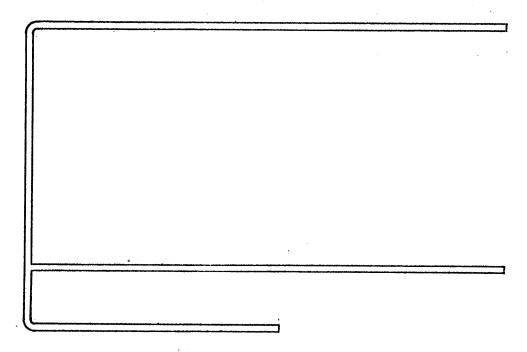

- (a) CONVENTIONAL UNIT CHASSIS. The Central Computer uses a total of 335 conventional unit chassis of 245 different types. A typical conventional chassis is shown in Figure 2-3. The chassis consists of a prepunched aluminum (Continued on Page 9)

| 13                                        | 1 | 2 | 3 | 4  | 5           | 6            | 7 | 8 | 9 | 10 | 11 | 12 | 14                |

|-------------------------------------------|---|---|---|----|-------------|--------------|---|---|---|----|----|----|-------------------|

| F<br>U<br>S<br>E<br>B<br>O<br>A<br>R<br>D |   |   |   | Co | DNVF<br>CHA | enti<br>Assi |   | L |   |    |    |    | F U S E B O A R D |

(a) Conventional Section, Front View

| 38      | 1  | 2  | 3  | 4  | 5          | 6    | 7  | 8  | 9         | 10 | 11 | 12 | 37      |

|---------|----|----|----|----|------------|------|----|----|-----------|----|----|----|---------|

| ۴       |    |    |    |    |            |      |    |    |           |    |    |    | - Z D - |

| USEBOAR | 13 | 14 | 15 | 16 | 17<br>PRIN | iter | Ì  |    | 21<br>JIT | 22 | 23 | 24 | CAHOR   |

| D       | 25 | 26 | 27 | 28 | 29         | 30   | 31 | 32 | 33        | 34 | 35 | 36 | PANEL   |

(b) Printed Circuit Section, Front View

Figure 2-2. Typical Sections of Central Computer

Figure 2-3. Typical Conventional Chassis

(Continued from Page 6)

channel with mounting positions for fourteen vacuum tubes. These positions are numbered one to fourteen. Mounted on the channel with  $4 \frac{1}{2}$  inch spacers is a terminal strip with 87 numbered tapered-contacts. Between the terminal strip and the channel are two component boards, mounted back-to-back. Along each long edge of the boards is a row of 52 mounting lugs, numbered 1 to 52. There may also be lugs along the center line of each board. The three rows of lugs on one board are designated J. H and K, respectively; those on the other are designated M. L and N. Components are mounted between lugs of like number on each board. The small components, such as diodes, are mounted between a center lug and an outer one; the large components, such as resistors and capacitors, are mounted between two outer lugs of like number. The component numbers are derived from their mounting positions: RN42 is a resistor (R), one end of which is connected to lug 42 of row N; CRM18 is a diode (CR). one end of which is connected to lug 18 of row M. Only low-wattage components are mounted on these component boards, since cooling is not effective in this area of the chassis.

The chassis are mounted on the bays in such a position that the vacuum tubes are located directly in the stream of cooling air. A maximum of four additional component boards can be mounted on the tube channel in such a location as to take advantage of the air stream. These additional boards accommodate high-wattage components which must be cooled. The boards are mounted on the right side of the tube channel, perpendicular to the channel. The seven possible locations for the boards are designated A through G.

Each external component board has two rows of 8 lugs. The lugs in one row are numbered 1 through 8; those in the other row are numbered 11 through 18. The components are mounted between corresponding lugs in each row; the component numbers are derived from the mounting positions, with the number of the outer

lug usually assigned to the component. As an example, RC12 is the resistor (R) connected between lugs 2 and 12 of component board C.

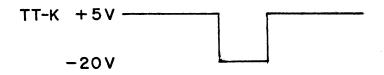

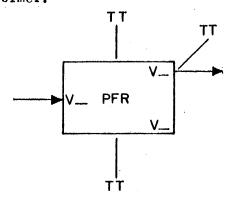

When the chassis is in position within the bay, the lugs of the external component boards are accessible for use as test points for meter and scope readings. Many important signals, such as gate and flip-flop outputs, appear on the test terminals. The test terminals are called out on the schematic diagrams, and circuit diagrams and the associated component board and lug numbers are also identified. (Example: TT E15 is lug 15 of component board E of a unit chassis.)

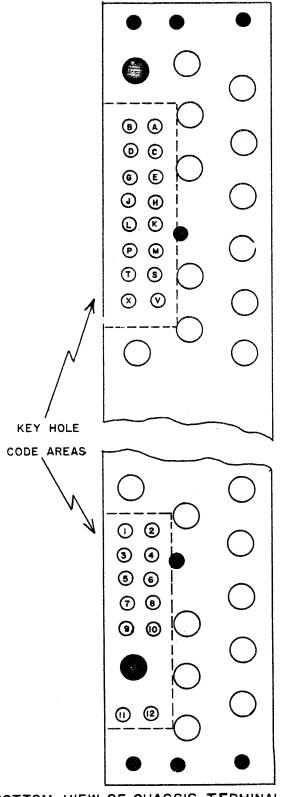

The tapered contacts of the terminal strip of each unit chassis mate with receptacles mounted on the section backboard of the computer. In order to identify each chassis of the Central Computer and to prevent its insertion into a wrong location, a system of coded key pins and holes is used. The key pins are mounted in the chassis terminal strip while the holes are contained in the section backboards. The location of the key pins and holes on a chassis is shown in Figure 2-4. The codes for all the chassis of the Central Computer is listed on Drawing XD142410. Just ahead of the number one terminal of the backboards are alphabetic positions, one for each bay plus S for Servo and T, V and X to designate the sections. At the other end of each backboard are 12 numerical positions where the chassis number is specified. Thus, a chassis with holes in positions B, T and 12 can be mounted only in the position whose pins are spaced accordingly. Duplicate chassis are exceptions to this rule.

Double-width chassis are used in the Central Computer when it is necessary to mount components which will not fit on a single-width chassis. The following chassis are double-width:

Al&2T, Al&2X, Bl&2X, ClO&11TX, Dll&12TX, H3&4V, and P3&4V.

(Continued on Page 12)

(BOTTOM VIEW OF CHASSIS TERMINAL BOARD)

Figure 2-4. Location of Key Holes on the Conventional Chassis

#### (Continued from Page 10)

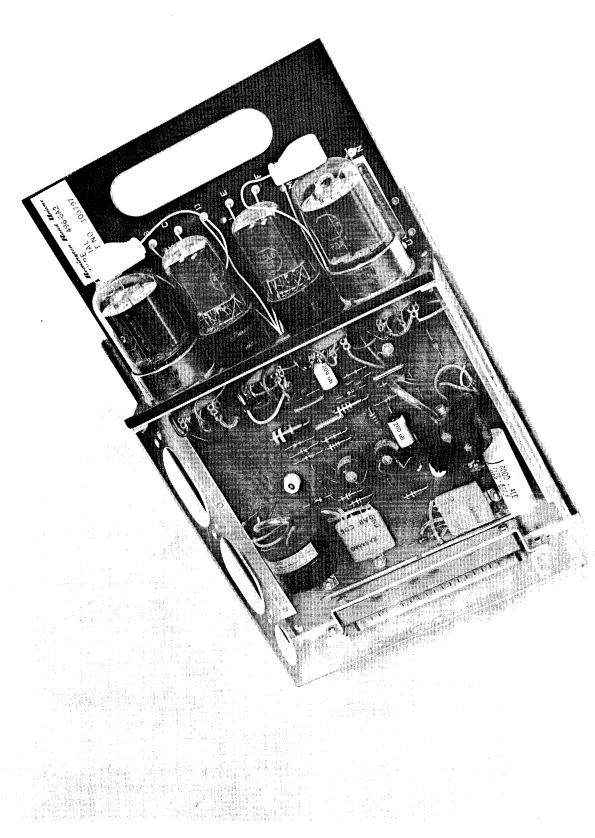

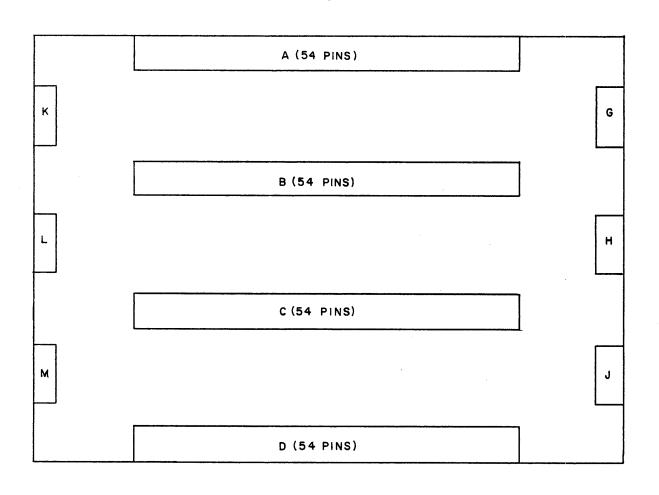

- (b) PRINTED CIRCUIT CHASSIS. The Central Computer uses a total of 310 printed circuit chassis of 29 different types. A typical printed-circuit chassis is shown in Figure 2-5. A prepunched channel has mounting positions for four or five vacuum tubes. The printed circuit board is mounted perpendicular to the channel. The printed wiring is on one side of the board, while the components are mounted on the other. A 33 pin connector is mounted at the end of the printed-circuit board which is opposite the tube channel. This connector mates with the appropriate jack mounted on the section backboard.

- (c) OTHER UNITS OF THE CENTRAL COMPUTER. The units of the Central Computer, other than the unit chassis which were described in the preceding paragraphs, are listed in Table 2-2. The designation of each unit is provided in the table, along with a short description of the unit. (Continued on Page 22)

TABLE 2-2. UNITS OF CENTRAL COMPUTER

| Unit       | Designation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

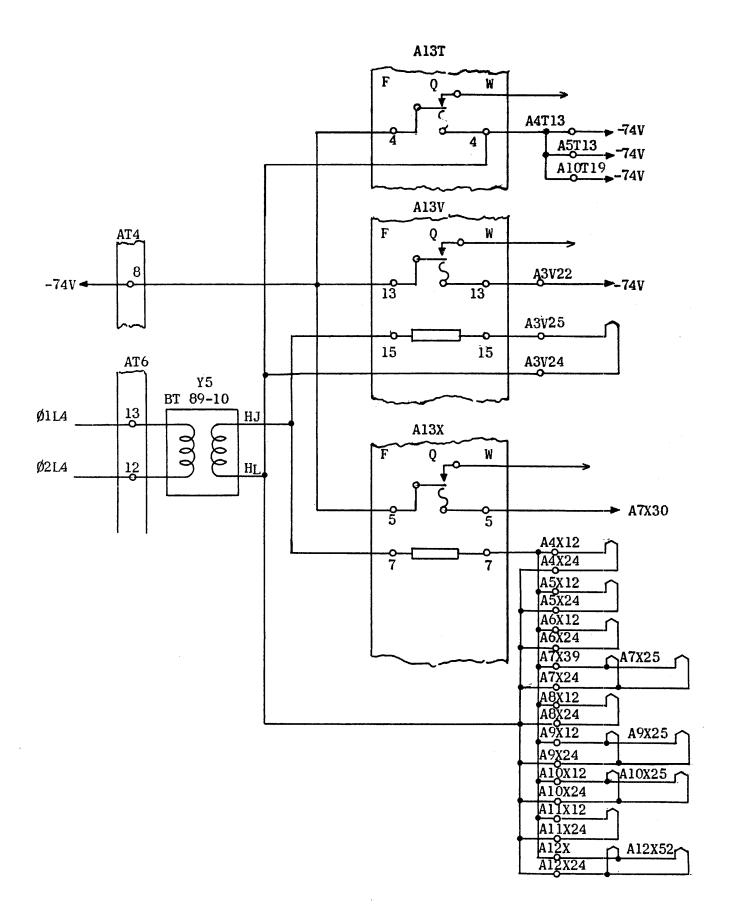

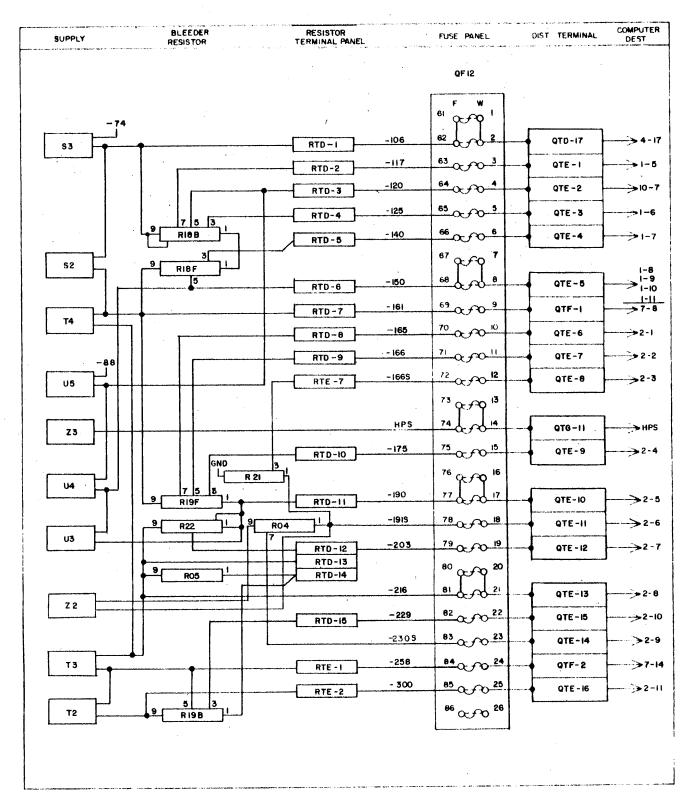

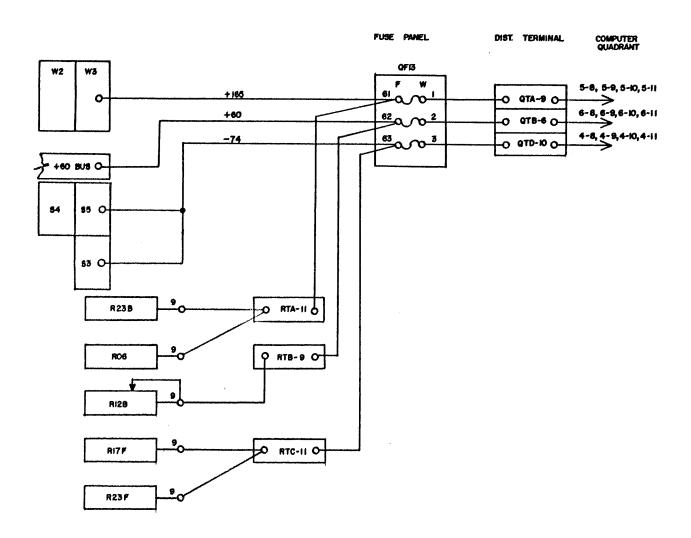

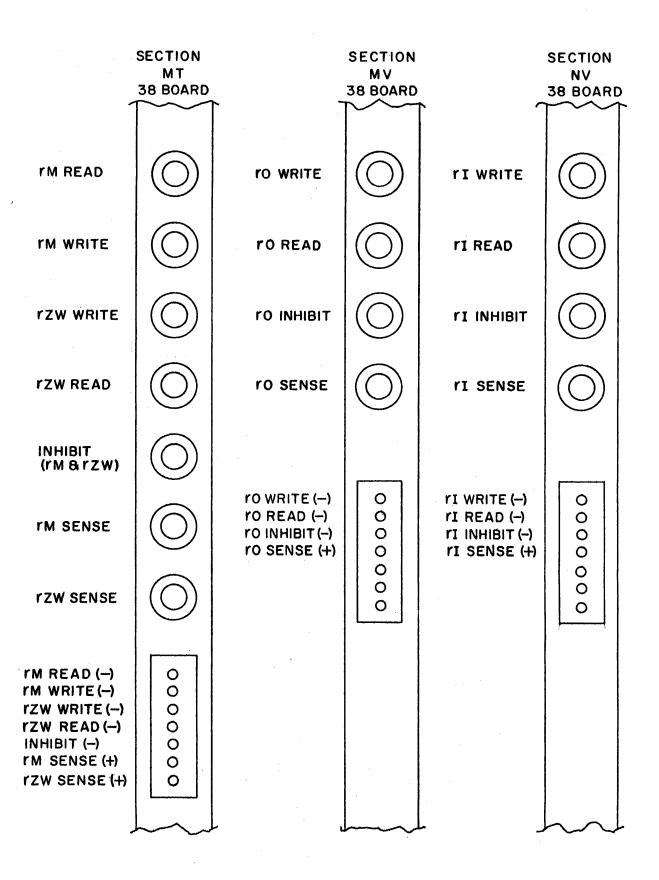

| Fuseboards | The left-hand and right-hand fuseboards of sections T, V and X of bays A,B,C,D,H,J,K L,P and sections GT and GX are designated as units 13 and 14, respectively. The fuseboards of sections T, V and X of bays E, M and N and section GV are designated as unit 38. The six additional fuseboards of bay P, which are mounted along the side nearest the access door, are designated as units 15 and 16 (in each section). (The complete designation of each fuseboard consists of the unit designation preceded by the bay designation and followed by the section designation.) | Each fuseboard contains 26 pairs of terminals, numbered from 1 to 26. The input terminals are labeled F and the output terminals are labeled W. Thus Al3T-F25 is the input terminal of fuse-position 25 of fuseboard Al3T. A center terminal, labeled Q, is also available for the alarm contacts of grasshopper fuses. Each fuseboard has a plastic cover to prevent personnel from coming in contact with the voltages. When the cover is properly in place, ter- minals 27 and 28 of the fuse- board are connected together. These terminals are wired into the interlock circuit of the Central Computer. |

Figure 2-5. Typical Printed Circuit Chassis

TABLE 2-2. UNITS OF CENTRAL COMPUTER (Cont 2d)

| Unit                                 | Designation                                                                                                                                                                                                                                                                                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |